3 PROFIBUS-DP智能从站设计

3.1 系统设计

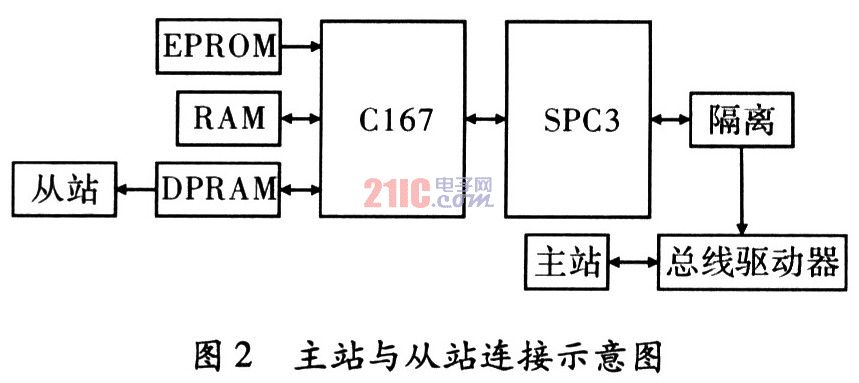

从站与主站之间的通信连接示意图,如图2所示。图2描述了主站与从站的连接。可以看出SPC3作为一个重要的媒介连接主站与从站,其数据交换的标准为RS485。

3.2 硬件电路设计

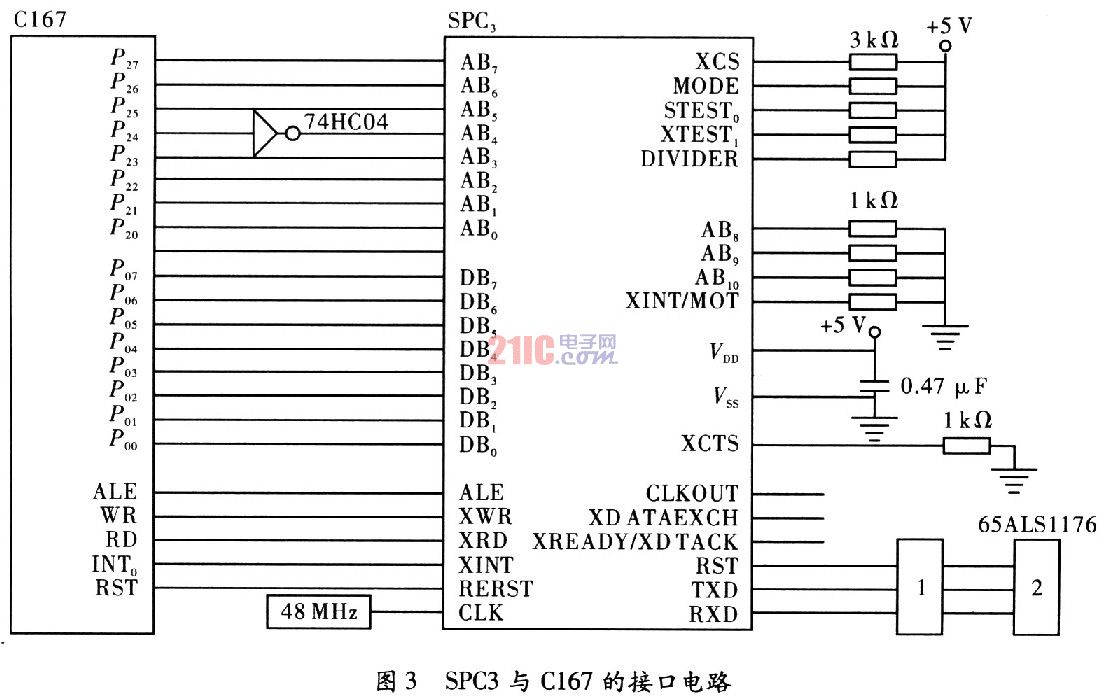

图3为C167与SPC3的接口电路。SPC3通过一块内置1.5 kB双口RAM与CPU接口,它支持多种CPU。SPC3中双口RAM的地址为1000H~15FFH。

SPC3的AB7~AB0管脚为地址总线,DB7~DB0管脚为数据总线,ALE管脚是地址锁存使能,XWR管脚为写信号,XRD管脚为读信号,XINT管脚用于进行中断控制,RESET管脚的功能是接CPU RESET输入,CLK管脚为时钟脉冲输入,所接的时钟频率为48 MHz。SPC3的右侧XCS管脚的作用是进行片选,XTEST0和XTEST1管脚必须接5 V电源,DIVIDER管脚是用来设置CLKOUT的分频系数,AB8~AB10管脚为地址总线,VDD接5 V电源,VSS接地,CLKOUT管脚为分频时钟脉冲输出,XDATAEXCH管脚为PROFIBUS-DP的数据交换状态,XREADY/XDTACK管脚为外部CPU的准备好信号,TXD管脚是串行发送端口,RXD管脚为串行接收端口。

C167的P27~P20管脚为地址总线,P07~P00管脚为数据总线,ALE管脚的功能是地址锁存使能;WR管脚的用途是外部数据存储器写信号,低电平有效;RD管脚的用途是外部数据存储器读信号,低电平有效;INT0管脚为外部中断0,低电平有效;RST管脚的用途是复位,当晶振在运行中,只要复位管脚出现2个机器周期高电平即可复位,内部有扩散电阻连接到VSS,仅需要外接一个电容到VCC即可实现上电复位。

图3中的模块1为光电隔离,模块2为驱动器,SPC3过光电隔离后与总线驱动器相连,具体的连接电路,如图4所示。

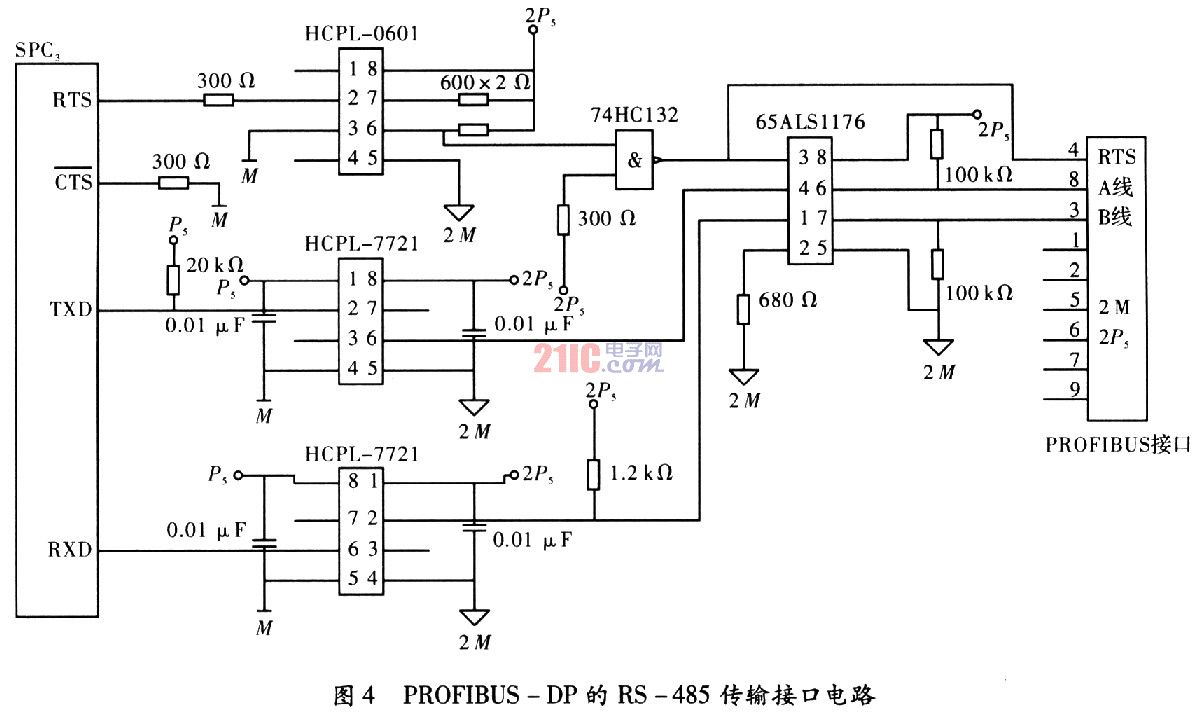

图4为PROFIBUS-DP的RS-485传输接口电路。其中,M和2M为不同的电源地,P5,2P5为两组不共地的+5 V电源。74HCl32为施密特与非门。RS485总线驱动器一侧与9针D型插座相连,另一侧通过光耦与SPC3相连。HCPL-0601和HCPL-7721是能够满足12 MB・s-1波特率的光耦,采用光电隔离主要是为了消除来自外界的干扰。