摘 要:串行外设接口SPI是现在很流行的一种同步串行接口,可用于与其他外设或者单片机进行通信。根据SPI总线性能特点,给出了SPI总线的数据传输规范,设计了一种SPI的IP功能模块,并成功应用到监控系统SOC芯片中。

1 引 言

SPI(Serial Peripheral Interface)串行外围接口是一种3线同步串行全双工通信接口,它具有电路简单,速度陕,通信可靠等优点,近年来大量的新型器件如LCD模块、FLASH、EEPROM存储器、数据输入输出设备都采用了SPI接口,新型的单片机一般都已将SPI接口控制器集成在单片机内部,这样能够大大降低软件的工作量。

由于SPI系统总线一共只需3~4位数据线和控制线即可实现与具有SPI总线接口功能的各种I/O器件进行接口,而扩展并行总线则需要8根数据线、8—16位地址线、2~3位控制线,因此,采用SPI总线接口可以简化电路设计,节省很多常规电路中的接口器件和I/0口线,提高设计的可靠性,使用SPI总线可以增加应用系统接口器件的种类,提高应用系统的性能。

2 SPI模块的接口信号、时序要求及工作模式

2.1 内部总线接口

在本设计中,内部总线接口采用的是AMBA总线3.0协议,具有较好的可移植性和可复用性。SPI是APB总线上的Slave模块。APB总线的时序完全遵照(ABMA Specification)(Rev 3.0)。因此此SPI模块支持3种DMA操作,除了标准信号线外,还有3根与DMA模块连接的中断请求信号线。

2.2 SPI总线接口及时序

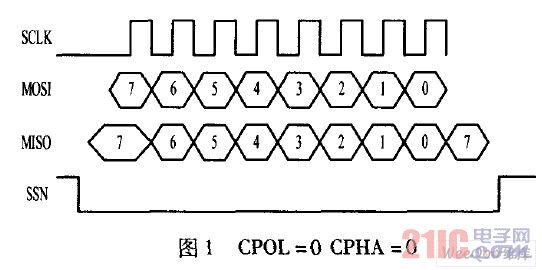

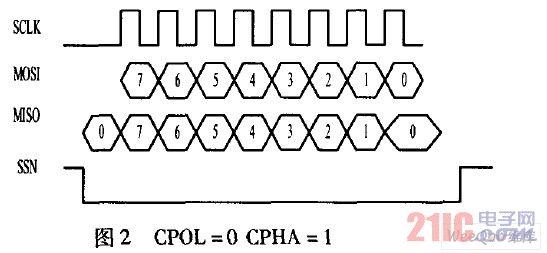

SPI串行接口使用4条线可与多种标准外围器件直接接口:串行时钟线SCLK,主机输入/从机输出数据线MISO,主机输出/从机输人数据线MOSI和低电平有效的从机选择线SSN。SCLK是主机时钟线,为MISO数据的发送和接收提供同步时钟信号。

在正常工作的时候,主机的4个引脚应和从机对应的4个引脚分别相连。

SPI模块为了和外设进行数据交换,根据外设的工作要求,其输出串行同步时钟的极性和相位可以进行配置,时钟的极性(CPOL)对传输的协议没有重大影响。如果CPOL=0,串行同步时钟的空闲状态为低电平;相反,如果CPOL=l,串行同步时钟的空闲状态为高电平。时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。

如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。SPI主模块和与之通信的外设时钟相位和极性应该一致。SPI接口时序如图1、图2所示。

图1 CPOL=0 CPHA =0

图2 CPOL=0 CPHA=1