���û��Cache��Ӱ�죬���Ӧ����55 aa aa���ɼ���Cache�ر��ٴ�ȷ�����Cache���ݹ�ʱ��

3 ����CPU�������Atmel��˾��

AT91RM9200��Samsung��˾��S3C44B0����������CPU�Ⱥ���ֲ������ϵͳ�����ڶ�������ʵ�����������Cache����ʹ�ܵġ����ǵĽ��������ʲô��?

AT91RM9200��ARM9ϵ�д���MMU��CPU��MMU���ڴ��з�ҳ�������ܣ�����ʵ�ֶ�����̵��ڴ�ռ䱣����Cache��ͨ��MMU�����ģ���Ҳ��Cache��MMU����ͬʱ���ڵ�ԭ��

S3C44B0��S3C4510Bͬ������Samsung��˾��Ʒ�����Ҷ�����MMU����S3CA510��ͬ���ǣ�S3C4480�Դ���SFR�������÷ǻ��淶Χ����ʹCacheʹ�ܣ������÷�Χ�ĵ�ַ�ռ����Ҳ��ͨ��Cacheʵ�֡����������Ժܷ����ʵ���ڴ��ǻ����������������Ƿǻ�������

�����ַ�������S3C4510B����ʵ�֡�������������volatile�ؼ��ֽ������������⡣volatile�ؼ�������Դ�����и����������ģ�������Ӱ��������ı���������������CPUִ�ж����ֵ������䣬��������䶼���ܽ��Cache���⣬volatile���Ҳ�Dz����ܽ���ġ�

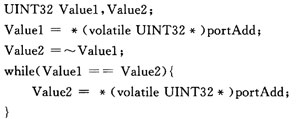

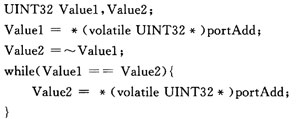

�����ױ����ݵ�����ʹ��volatile�ؼ�����Ӧ�õģ��ɱ�����������Ż�������������䣺

�����ζ�ȡportAdd��ַ��������ͬʱ�ȴ��������õ��ȴ��ź�����ij��������volatile�ؼ���ȥ�����п��ܾ��������Ż���Value2�����ʵ�ʵ�portAdd��ַ��ȡ���ݣ���������Valuel��ȡ�����м�Ĵ���ֱ�ӻ�á�

4 ���Ľ��������S3C4510B�ֲ��ϵ�5�ڵĵ�4ҳ��֪������ͨ�����ַ�ʽ��֤Cache���ݵ���ȷ��

�ٶ�Cacheӳ�����Tag RAM�������㡣Cacheӳ�������һ����ͨ���ϵ縴λ����ģ����Cache���ڴ�ε����ñ��ģ�������Cacheӳ������ݷ�������ʱ����Ҫͨ�������Cacheӳ���������0��

��S3C4510B�ṩ��Cache��ʽ���ʿ���λ������λADDR[26](��ַ��26λ)Ϊ��1��ʱ������Cache��ʽ���ʡ���ˣ�Cacheʹ�ܵ�����£���ַ0x000 0000��0x3FFFFFF��Cache��ʽ���ʣ���0x400 0000��0x7FF FFFF����Cache��ʽ���ʡ�ʵ���ϣ�0x000 0000+offset��0x400 0000+offset(offset��0x000 0000��0X3FF FFFF֮��)��ͬһ��ַ����ͬ����Cache�Ƿ������á�

���Եõ����ֽ�������� (1)Cacheӳ����ֶ����� ��Ȼ�ڿ���Cache֮�����ݹ�ʱ������CPU�����Զ�ˢ�£�����ͨ���ֶ����µİ취�������Ͼ���Ϣ��Ҳ����˵����Tag RAM��(ǰ����˵��Cacheӳ���)�������������Cache�����������ݶ���ʹ�ܣ��ٴζ�ȡ����ʱͬʱ����Cacheӳ�����Cache���������ݣ�֮�����ʹ�á����������Tag RAM��1 KB�������㣬��Ҫ����һ��ʱ�䣻��������������Cache��0�����ʵģ�ֻ��һ�����ʴ�����Cache��Ϣ�������������ָܻ������������ʡ���ˣ�Ƶ���ؿ���Cacheʱ�������ַ����Dz���ȡ�ġ�

(2)bit26λ����Cacheʹ��

S3C4510B�ĵ�ַ��Ϊ26λ(bit0��bit25)��ʵ����CPU�ɷ��ʿռ�Ϊ32λ(bit0��bit31)��һ�����Ƕ���ʹ��bit26��bit31������S3C4510B����Щλ��������Ŀ��ƹ��ܡ�ͨ��bit26�ĸߵ�ƽ���Խ�ֹ�õ�ַ��Cache���ܣ���˽�����ĵ�ַ��ԭ����ADDR_PORT��Ϊ(ADDR PORT�O(1<<26))���Ϳ���ʵ���������ʱCache��ʹ�ܡ������Ͳ��ø�ΪSYSCFG��Cacheʹ�ܿ���λ���Ƚ�������SYSCFG��Cacheʹ��λ�ǿ�������CPU���ʵ�Cacheʹ�����bit26ֻ���Ƶ�ǰ���ʵ�һ�������ַ��Cacheʹ����������ֽ�����������������ݣ����ҿ������̶ȷ���CPU�Ĺ��ܡ�

5 �ij�������������Cache����������Խ���ڴ���ʴ�������⡣�������ԣ����á�bit26λ����Cacheʹ�ܡ��ķ�������˳���������裬����ִ��ʼ������Cacheʹ�ܵ�����£����Ҳ�Ӱ���ڴ����ݡ�����ȫ�ر�Cache�ij���ִ��ͬ��������Ҫ����5��8����ʱ�䡣

��һҳ [1] [2]