1.3 时钟电路

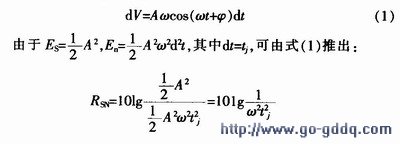

中频采样系统的时钟抖动会对系统性能产生很大影响,并且随着输入信号频率的增加,这种影响越来越明显。设输入信号V=Asin(ωt+ψ),采样时钟抖动为dt,信号能量为Es,噪声能量为En,则有:

式(2)是在假设信号为正弦信号输入的基础上推导出来的。而对于任意信号,都可以看成是单频(正弦)信号的组合,所以,式(2)具有通用性。因此,在已知输入信号频率fin及采样时钟抖动tj的情况下,A/D转换器的信噪比被要求限制在-201g2πfintj以下,该信噪比与采样时钟fs无关,却与输入信号的频率fin相关。

2 系统硬件设计

2.1 A/D转换电路设计

采用AD9445作为A/D转换电路的核心器件.该器件是一款适用于中频采样的14位,单片集成A/D转换器。它采用3.3 V和5.0 V双电源供电,支持差分信号的时钟输入,支持CMOS、LVDS 2种数据输出格式。其重要引脚功能如下:DCS MODE:时钟占空周期稳定器控制引脚,该引脚为低电平时可以起到稳定时钟周期占空比的作用。

OUTPUT MODE:将输出数据电平选择为CMOS电平,或者LVDS电平,为了获取更高的性能,采用LVDS电平。

DFS:数据格式选择。可以将输出数据格式设置为二进制补码或者偏置二级制格式。

VREF:配置该引脚可设置其内部参考电压。

SENCE:配合VREF引脚完成内部参考电压的设置。

REFT,REFB:差分参考输出引脚。

VIN+,VIN-:输入电压引脚。

CLK+,CLK-:采样时钟输入引脚。

D0~D13:输出引脚。

DC0:数据时钟输出引脚。

目前,主流中频采样A/D转换器都采用差分信号输入。差分信号能有效地去除共模噪声。提高系统的抗噪声性能。这里采用LVDS模式的差分信号输入。电路设计如图2所示。经过调试。本系统在输入中频单频信号频率为40 MHz的情况下。信噪比可达77.4 dB,,其频谱如图3所示。

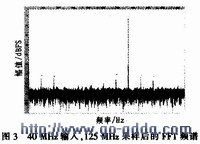

2.2 A/D转换器前端运放电路

该系统设计采用AD8352型超低失真差分中频放大器作为A/D转换器的驱动器件。其电路设计如图4所示。

通过设置电阻RG的大小,可调节AD8352的放大倍数,其范围为:3~25 dB。CD和RD用于消除失真。通过前端的变压器,可以将单端信号转换为差分信号,为AD8352提供差分信号,使其具有更高的性能。