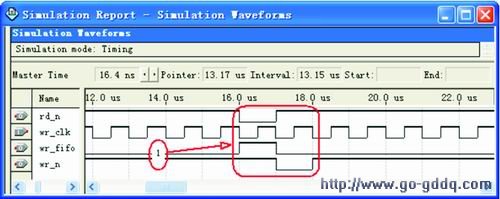

当系统加电后,wr_n输出一个有效的写信号启动A/D转换,经过足够的时间后(T=327μs~328μs),输出读信号,此时数据接口单元的写允许信号wr_fifo变为有效,同时外部A/D转换器的读允许信号也变为有效,此后 ADC 0804的数据端口上输出有效数据,在wr_clk的上升沿将A/D转换器的数据读入FIFO。控制逻辑单元的时序仿真图如图5。

由图5可知,wr_fifo有效时,ADC0804必须在wr_clk的上升沿到来之前在其数据端口输出有效的数据。由于wr_clk的周期为1ms,ADC0804的输出锁存由其读引脚rd控制,rd变为有效即可输出有效的数据,故只要ADC0804的读信号rd在外部输入的作用下变为有效的时间不超过500ns,读操作就不会出现问题。ADC0804的rd信号三态延时最大为200ns,典型值为125ns,因此控制信号产生逻辑单元满足要求。

图5 控制信号时序仿真

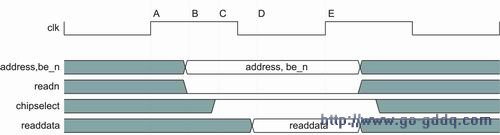

当NIOS系统需要读取数据时,在read和readclk上出现的是系统AVALON总线上的读时序。时序图如图6。

图6 基本从端口读传输

在AVALON总线中定义了两种类型的信号,一种是高电平有效,另一种是低电平有效。在本设计中选用的是高电平有效的类型。图6是低电平有效的总线信号,与之对应的高电平有效的总线信号时序图中,read在有效时为高电平对应于图6中的readn的低电平部分。而address,be-n和Chipselect在此可以不与考虑,添加到AVALON总线时,系统会自动处理其连接问题。

当系统不读取A/D转换的数据时,采集的数据由数据处理单元控制处理。数据处理单元实现了对外部信号量的异常检测,即,当外部信号的幅值超出设定范围时,该单元产生一个

结语

经测试,本设计可以不间断无数据丢失的进行数据采集,CPU可以主动的读取数据,也可以在数据处理单元检测到外部异常信号时被动的获取数据,并且CPU读取数据的操作极其简单,运行时只占用很少的CPU资源,在此,谨希望本文能在如何设计NIOS系统外设方面给读者以参考借鉴。