技术趋势

除了新颖的电路设计技术,工艺的进步在 低功率 高速 ADC的开发中同样重要。特别值得一提的是,由于数字技术最初的驱使,硅技术工艺不断调整,采用CMOS工艺制造的ADC也因此受益匪浅。

就模拟电路设计而言,CMOS工艺调整的关键优势在于更低的功率和更高的速度运作。与仅消耗动态功率的传统数字CMOS电路不同,ADC消耗的大部分功率都是静态电流用来偏置放大器和比较器等模拟电路引起的。对给定的模拟偏置电流,更短的通道长度(L)工艺为晶体管提供更高的跨导(gm),这是器件性能的一个关键衡量指标。更小的晶体管尺寸也使器件的寄生电容更小。在高速ADC的每一种流水线级上,精确运算放大器等关键电路的模拟稳定速度极大程度上由晶体管gm决定。因此,在给定总偏置电流情况下,缩短L会使工作速度更快。

然而,模拟电路的工艺调整存在一个严重的缺点。由于降低了电源电压,ADC的满标度输入范围也必须降低,以便为运算放大器等模拟电路系统提供足够的电压空间。更小的输入范围导致更低的信号功率,SNR会随着工艺调整而下降。低功率、高性能设计方案的挑战还在于降低ADC产生的噪声,以保持足够的信噪比。

凌特公司低功率高性能ADC介绍

很明显,低功率、高性能是市场上用户的主要要求。为满足市场需求,凌特公司新近推出了几个高速ADC系列。

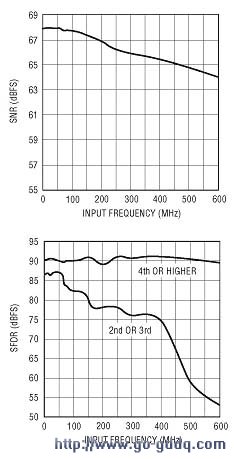

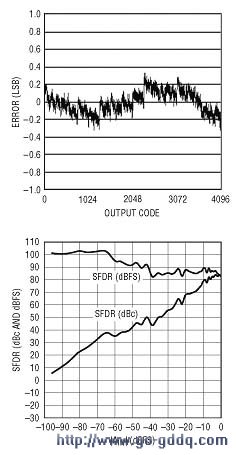

LTC2224/2222/2223是引脚兼容的3.3V 12位135/105/80MSPs ADC,并为欠采样而优化。LTC2224系列在输入频率高达140MHz时具有超过67.5dB的SNR和80dB的SFDR,而在135Msps时仅消耗630mW功率。该高度优化的跟踪与保持设计对高达400MHz的输入频率持续保持超过65dB的SNR和75dB的SFDR,在低功率时具有极佳的欠采样性能。图2概括了LTC2224的高频性能。即使是那些消耗功率高得多的器件也极少在高输入频率时具有如此的欠采样性能。如图3所示,就12位ADC而言,该ADC转移函数的线性度也很高,可与很多14位器件媲美。如同干净的转移函数预料,小输入幅度时的失真性能也相当稳定。LTC2224系列非常适合要求低功率和卓越欠采样性能的WCDMA PA线性化应用。

图2

图3

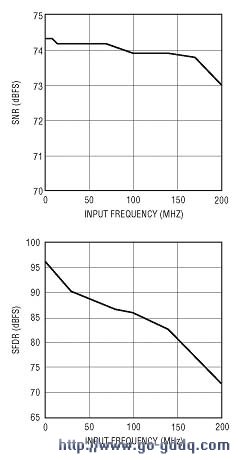

LTC2249/LTC2229系列是引脚兼容的3V 14位/12位ADC,具有高达80Msps的速度。表1概括了这些器件的性能特性。这些高速ADC功率极低,范围从LTC2249/LTC2229在80Msps时的222mW至LTC2245/LTC2225在10Msps时的60mW。实现这些低功率并未损失性能。例如,如图4所示,LTC2248(65Msps)对远离奈奎斯特频率(Nyquist Frequency)的输入保持为74dB SNR和80dB SFDR。通过使用5mm×5mm纤巧型QFN封装,这两个系列还实现了小体积。大部分必需的旁路电容都直接集成在芯片上,因此这些器件仅需要少量低值外部旁路陶瓷电容器,就能达到数据表所显示的性能。引脚兼容的LTC2249和LTC2229系列具有高性能,低功耗,小体积的特点。使它们非常适合用于小型WCDMA、GSM和TD-SCDMA等基站。

图4

表1

结论

都市基站 设计方案在高输入频率和宽输入带宽时要求良好的SNR和SFDR性能。这样就需要有高线性度的跟踪与保持设计以及小内部采样时钟抖动;每一方面在ADC中都需要消耗功率。很多低功率ADC的SNR和SFDR都随着输入频率的提高而迅速下降,因为内部时钟抖动和跟踪与保持电路的非线性主要影响了响应。但是,最近推出的低功率和小尺寸的高性能ADC克服了这些问题,满足了新一代无线通信市场对尺寸更小、功率效率更高产品的需求。