嵌入式设备在DSP中实现嵌入式设备还比较少,一般DSP都直接集成这些设备模块,用户选择不同型号的DSP芯片以满足产品应用要求。但对于一些较为特殊的嵌入式设备,DSP也可以实现该功能。本文以dMAX和EMIF接口的数据传输为例,介绍嵌入式FIFO的设计、配置及其使用。

dMAX及其结构

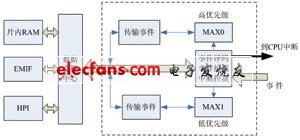

dMAX(Dual Data Movement Accelerator,双向数据传输加速器)是TI公司的DSP芯片C6727B特有的一种片内设备。应用dMAX和EMIF(External Memory Interface,外部存储器接口)可以实现片内RAM、片内和片外设备以及两个片外设备之间的数据传输。dMAX模块的内部结构如图1所示。

图1 dMAX内部结构图

从图中可以看出,dMAX主要由事件和中断处理模块、事件编码器、传输事件模块等组成。事件模块分成高优先级和低优先级两个相互独立的模块,各自有独立的事件入口和事件参数表,和CPU有独立的接口。使得dMAX可以同时处理两个不同的事件。当访问CPU端口时,MAX0的优先级高,MAX1的优先级低。dMAX能够通过执行先进的一维、二维与三维数据的存储器传输工作,从而使DSP得以专注于信号处理任务,显著提高系统性能。适合图像的子帧提取或者语音信号的子信道提取。

DSP内部的数据交换中心在dMAX的控制下,可以实现片内RAM、EMIF以及HPI接口之间的数据交换。本文介绍在dMAX控制下,实现片内RAM和EMIF接口之间的数据交换。如果DSP采用普通的异步接口方式,数据传输需要建立、选通和保持3个阶段,最少需要5个EMIF时钟(建立和保持各1个时钟,选通3个时钟)。为了保证通信的可靠性,一般采用10个EMIF时钟(建立3个时钟,保持2个时钟,选通5个时钟)。而EMIF时钟最快为133MHz;这样,采用异步接口的通信速率一般为13.3M×32b/s(采用32位数据总线宽度)。此外,异步接口数据传输必须在CPU的参与下,使用指令实现数据搬移。将占用大量的CPU开销,在很多高速的数据采集和处理中,将降低系统的整体性能。为此,采用dMAX实现嵌入式FIFO数据传输克服异步传输的缺点,其传输采用突发读写方式进行,可以连续突发读写8个数据,一共只需要20个时钟,通信速率提高为53.2M×32b/s,提高4倍读写速率。还可以采用和DMA后台运行,这样将大大降低整个系统数据读写的开销,从而可以实现更加复杂和可靠的算法处理。

嵌入式FIFO设计

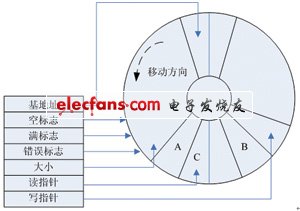

嵌入式FIFO的设计主要就是控制FIFO的7个参数。这7个参数分别为基地址、空间大小、空标志、满标志、错误标志、读指针和写指针。它们之间的关系如图2所示。

图2 FIFO结构示意图

基地址和空间大小用于规划出一段内存空间,该内存空间用于FIFO设备,并被FIFO设备保护起来,使得其他设备和程序不能访问该空间。为了便于操作方便,空间大小一般为2的整数次幂,但不做要求。具体到C6727B型号的DSP,空间大小最大为1M个元素,元素大小可以是8位、16位或者32位数据,不能为其他类型的数据。基地址可以为内存空间的任何一个地址,同样为了操作方便,一般为空间大小的边界点。例如,8个元素的FIFO,其基地址一般为XXXXX000b,也就是地址的低3位为0,基地址就肯定为8的整数次。同样,64个元素的FIFO,其低6位为0。基地址和空间大小的特殊要求避免访问时的地址跨越多页问题,可以提高FIFO的访问速度。

空标志和满标志用于表示FIFO的存储状态。读指针和写指针用于表示读写的当前地址。错误标志表示对FIFO的错误操作。当FIFO处于满标志情况下仍然写FIFO,或者FIFO处于空标志情况下仍然读FIFO,FIFO都将终止当前操作,并将错误标志置位。

FIFO的写操作只有一种工作方式,即每次写一个新的数据,写指针加1,直到写满。而FIFO读操作有两种工作方式,分别为标准操作和多阶延迟(Multi-tap Delay Transfer)操作。标准操作和写操作一样。多阶延迟操作一般用于滤波处理,当需要对输入信号进行滤波处理时候,每次希望从FIFO读取一段窗口的数据,进行滤波处理,数据窗口仍然只移动一个数据。在标准操作情况下,如果读取一段窗口的数据,FIFO则将该段窗口的数据全部弹出。多阶延迟操作则只弹出一个数据。该操作方法对语音或者AD采样数据的平滑、FIR等滤波非常适用。需要注意的是,多阶延迟操作的数据窗大小需要设置,如果FIFO存储的数据个数小于数据窗,FIFO则终止当前操作,并给出错误标志。