・上一文章:一种实时图像目标搜索与跟踪系统设计

・下一文章:松下MD2L机芯彩电资料

其中有效表示数据总线的高8位有效,SA0有效表示数据总线的低8位有效,作为译码信号的一部分,对于单片16位数据线的集成电路,实际上也可以不连接,用SA0和高端地址线译码产生选片信号。AEN信号有效表示计算机在和某个设备进行DMA传送,其他的设备发现AEN信号有效,就不要响应寻址信号。因此在CPLD内部逻辑里设置当AEN信号有效时,将进入CPLD的地址信号线置为高阻态。

![]()

是存储器读写信号,是用于1 M以外地址空间的读写信号,当这两个信号之一有效且寻址到1 M内的地址,将分别使1 M以内地址的读写

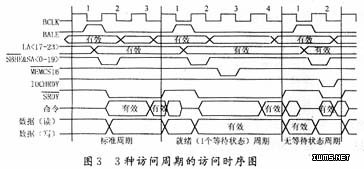

一起控制总线周期的长短。有3种存储器访问周期:标准周期,就绪周期,无等待状态周期。访问时序如图3所示。

?

在设计的时候考虑到信号在CPLD里的延时,如果标准周期对于访问的时间长度不够,可以采 用有1个等待状态的就绪周期,而这只需要修改CPLD的设计并重新下载到CPLD即可,由此可 见用CPLD作为控制芯片的优点。

4结语

本文说明的这种PC104总线与DSP的数据通讯接口设计,也可以作为采用其他计算机总线与DS P进行16位数据通讯接口设计的参考。