1) 帧同步: 在一些任务中需要帧同步(例如,通过以太网传输和接收时,当码流速度不断变化而解码器需要一个恒速的传输流)。虽然存储器对同步的要求似乎很小,但当涉及到多个码流时它可能很显著。这种同步可以由一个异步FIFO实现。

2) 帧存储: 帧存储在这些地方需要:任何暂时的处理如帧率转换,数码变焦(缩放),或执行去隔行。储存的帧数量随着需要的临时信息数目增加而增加。当视频数据按照本来的顺序时,帧缓存也必须是“先进先出”。

通过上面的讨论,我们可以说,所有的储存和同步都可以使用FIFO实现。那么理想的FIFO应该是多大的呢?一个典型的1080p 帧,10位 4:2:2格式将需要存储器大小为39.55M位(每行像素数*每帧行数*每像素比特数= 1920*1080*20)。预计总容量可以通过需要存储的帧数乘以这个数字。典型的视频处理算法需要存储2到3帧,这意味着总容量要达到120M位。由于不可能有如此大的基于片上SRAM的FIFO存储器,一般的方法是使用一个DRAM来缓存这个数据。

高密度FIFO -传统的实施和及其复杂性。

帧缓存就是高密度FIFO,传统上使用外部DDR SDRAM实现。举例说明一个典型的视频处理应用和这些FIFO如何实现。

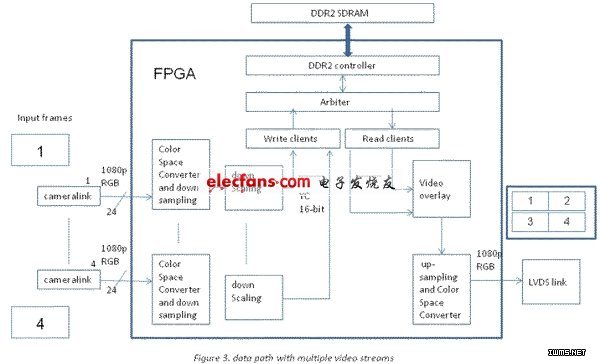

图3显示了一个典型情况的数据路径,有4种不同来源的视频流需要显示在同一个显示器上。四个以1080p60(24位RGB)分辨率捕捉视频的高清相机使用一个cameralink接口连接到系统上。色彩空间转换 (从RGB到YCbCr)及色度采样降低(从4:4:4到4:2:2)后,横向和纵向帧按比例减少,并储存在DDR2 SDRAM里。存储的帧可以按要求读回和定位,结果帧和融合帧然后提高采样速度和色彩空间转换为通过LVDS连接来驱动面板。

让我们看看存储器大小和带宽要求:

(i) 大小要求:

尽管这里没有涉及到时间处理,为了避免一个源的两帧被分开储存,这样当一帧正在写时,另一个帧可能要读回来。两帧图像的大小是((1920 * 1080 * 16)/ 4)* 2 ~ = 63.3M位。

(ii)带宽要求:

由于读和写路径为复用的,所需带宽是读、写路径带宽之和。

写路径频率=(每个客户端频率)*( 客户端数量)=(148.5/4 )* 4 = 148.5MHz

读路径频率=输出帧分辨率频率= 148.5MHz。

实际的工作频率为( (读频率+写频率) / 2 +其它开销),因为接口工作在双数据速率,并且还有一些其它开销,如DRAM存储器刷新周期、bank地址切换等等。假设为80%的效率,那么将在185MHz的频率运行。

(iii)内存接口大小和I / O需求:

当画面以16位4:2:2格式存储时,一个16位接口就足够了。根据计算,FPGA 的I/O总数的为46:

时钟引脚(2个用于差分时钟,1个用于时钟使能)= 3引脚

命令引脚(片选,RAS, CAS, WE)= 4引脚

地址引脚(14个地址线、3个 bank地址线)= 17引脚

数据线(X16接口)= 16引脚

数据选通及分离(4个引脚用于2微分DQS,2个用于分离数据)= 6引脚

高密度FIFO -离散的存储器:

现在让我们看看使用离散可编程高密度FIFO的实现方式和特性定义,这样DDR2 SDRAM存储器就可以由简单的数据存储便可以由简单的数据存储代替。

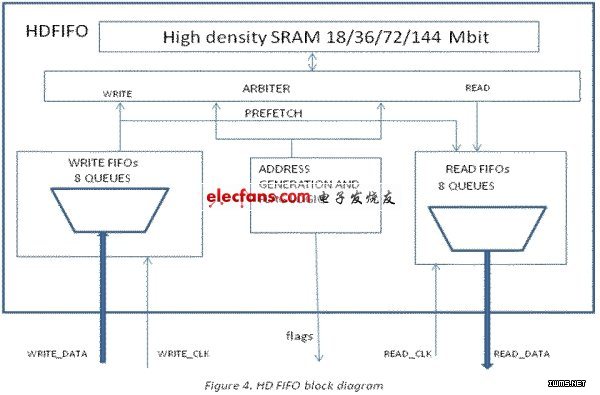

(i)多队列特点:

如果FIFO存储器定义为一个单一块的内存,那么写多个视频流是不可能的。因此,FIFO必须能够配置并分成多个队列。在上文的例子中,有四种不同的画面要写,并且四个帧必须同时从不同的队列同时。因此,我们的应用需要至少八个队列。

(ii)分离和重传:

有可能从一个标准的FIFO曾经读过的数据又从FIFO丢失了。FIFO指针可以重新编程,允许任何帧都可以根据需求多次读出。

图4显示了赛普拉斯CYFX072VXXX HD-FIFO的框图。

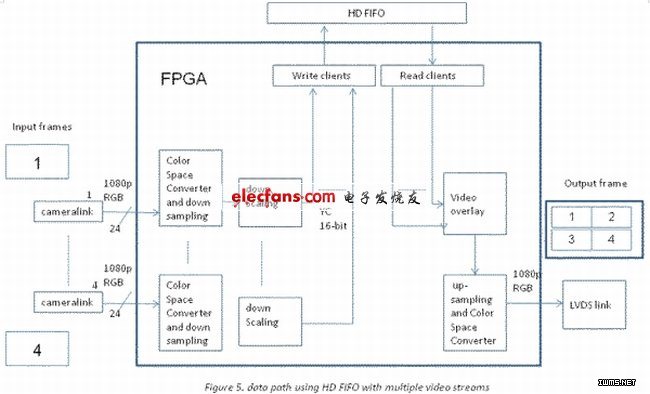

图5给出了使用赛普拉斯HDFIFO替代DDR2芯片的应用案例。