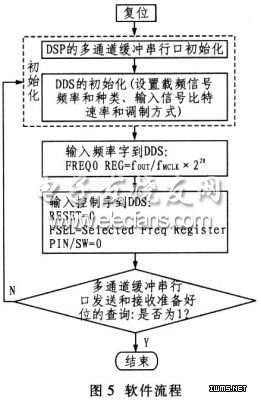

软件的流程如图5所示,主要包括复位、初始化、写频率字和控制字等部分。

初始化部分包括对DSP多通道缓冲串行口的初始化及其配置和对AD9834写入控制字,应设置多通道缓冲串行口工作模式和DDS的SLEEP、RE-SET、SIGNPIB、HLB等位。在该系统设计中,AD9834采用串行控制比特位方式选择相位、频率寄存器;PIN/SW=0.选择控制字模式;FSEI=0,选择使用频率寄存器0(FREQ0);D13=0,将28位的频率寄存器分成2个14位的寄存器工作,且频率字的高14位和低14位可以独立改变。由于系统要求在上电后立即工作,故将AD9834的RESET引脚接低电平。必要时,也可以由系统中的其他模块如CPID控制DDS启动。SDATA、SCLK和FSYNC 3个引脚向AD9834中写数据和控制字。当FSYNC=0时,表示正向AD9834写入1个新字,并将在下1个SCL.K的下降沿读人第1位,其余的位在随后的SCLK的下降沿读入,经过16个SCLK下降沿后,置 FSYNC=1,实现了DSP对AD9834的控制。

由于将C5410的McBSP配置为时钟停止模式,串口接收控制寄存器SPCRl的时钟停止模式位cLKSTP和串口引脚控制寄存器PCR的发送时钟极性位CLKXP配置为CLKSTP=11,CLKXP=1(时钟开始于下降沿,有延时),因此,发送时钟模式引脚设为内部时钟输出(BCLKX=I);采样率发生器时钟源来自CPU时钟(CLKSM=I);发送帧同步模式引脚设置为输出(FSXM=1);发送帧同步极性引脚设置为低电平有效(FSXP=1);发送时钟极性设置为下降沿采样 (CLKXP=1);数据发送和接收延时时间为l位(RDATDLY=XDATDLY=01b);采样率发生器时钟的降频因子为49(CLKGDV=49)。因为16xbaud rateCLKOUT/1+CLKGDV为100/49,所以MCBSP的采样率发生器产生2MHz的时钟信号。

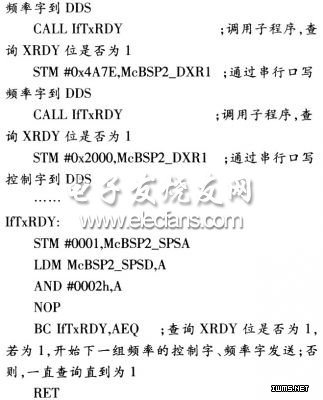

下面是通过McBSP口向AD9834传送频率为8.2MHz的频率字和控制字的程序段: L

程序设计中应该注意的重点就是对发送和接收准备好位的查询,如果在程序中没有查询或者查询的地点不对,则程序在单步运行时可能会正确发送和接收数据,但是当全速运行时,由于速度较高,因而不能进行正确的数据收发。正确的查询应该是在数据发送前查询SPCRl或SPCR2中的RRDY位或XRDY位,当RRDY位或XRDY位为0时,表明尚未接收或发送完数据,一直查询到RRDY位或XRDY位为1,表明上一组数据已接收或发送完毕,可以进行下一组数据的接收或发送。

5 结束语

由DDS技术产生的扫频信号源不仅频率稳定、信号精度高、抗干扰能力强,而且由于它是在计算机控制下直接实现的,因而易于实现智能化处理。在频率迅速变化的场合,DDS中寄存器更新的速度有时会成为关键指标,这时必须使用高速电路和高速串行口,由合理的硬件设计和软件流程来实现预期设计目标。