・上一文章:中宝ZB0-KB18A功放电路

・下一文章:台湾WHDI无线HDMI传输解决方案

3. 基于simulink的可逆分频器设计

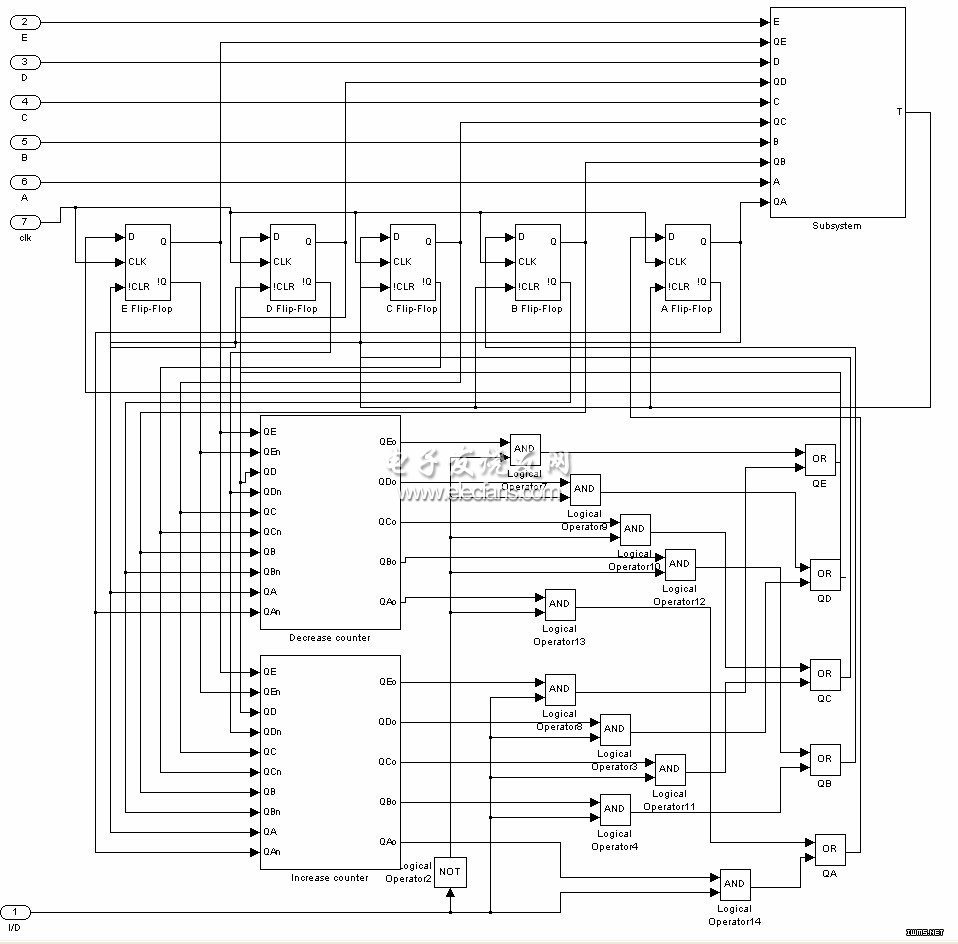

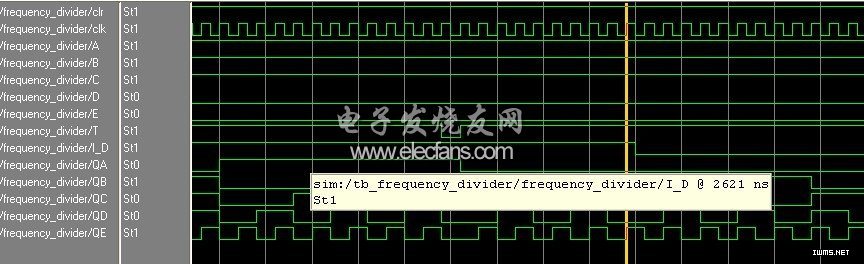

采用simulink 建立可逆分频器模型,如图1 所示。分频器采用五级D 触发器实现,辅之以必要的控制逻辑。输入端A、B、C、D、E 为输入模值,I _ D为1 时分频器工作在递增模式,当I _ D为0时分频器工作在递减模式,符合函数的输出T连接至D触发器的清零端,分频器的工作波形如图2 所示。从图中可以看出分频器能够在预置模下完成递增或递减分频器功能。

图1 五级分频器

图2 分频器的工作波形。

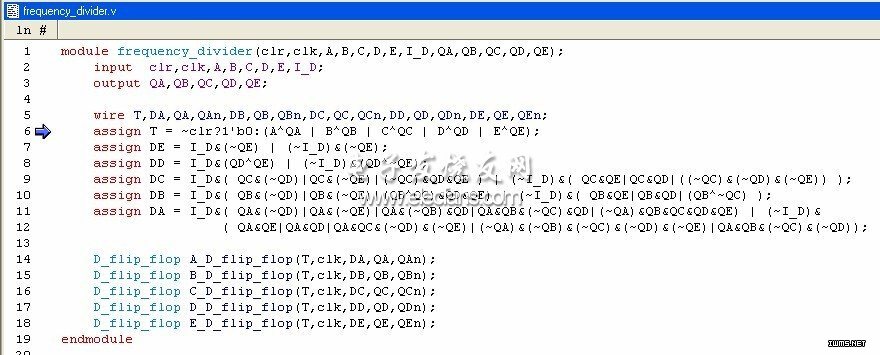

图3 分频器的仿真波形。

4. 基于FPGA的可逆分频器设计

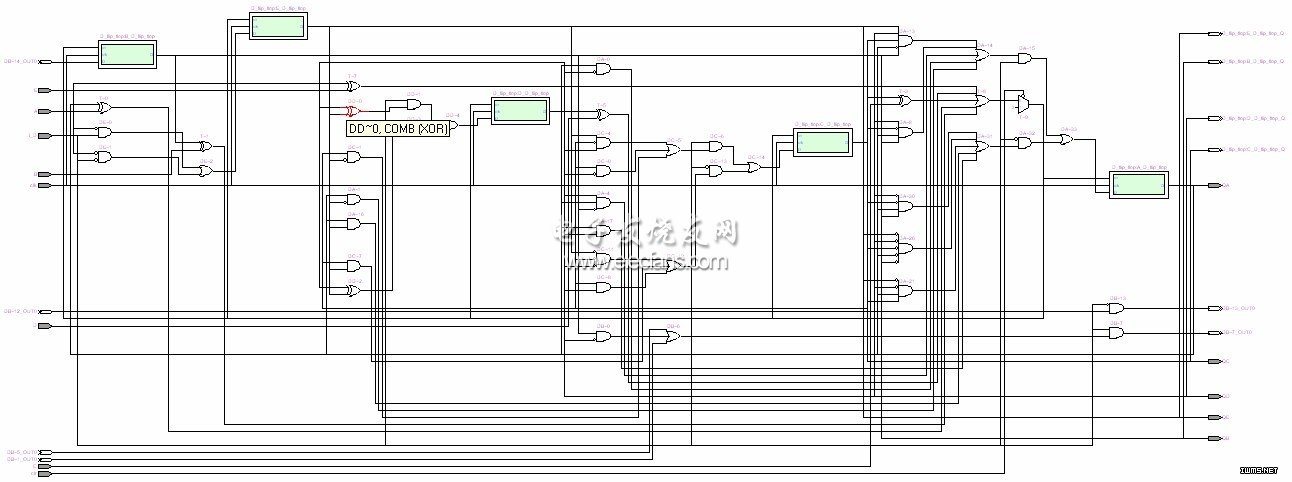

采用verilog 语言实现了可逆分频器,其仿真波形如图3 所示,分频器可完成预置模以及递增及递减分频功能。分频器的verilog 代码如图4 所示,寄存器传输级网表如图5 所示。

图4 分频器代码。

图5 寄存器传输级网表。

5. 总结

本文分析了变模可逆分频器的工作原理,并分别采用simulink 和FPGA 实现了可逆分频器。仿真结果表明分频器能够完成预置模,递增和递减分频功能,满足设计要求。