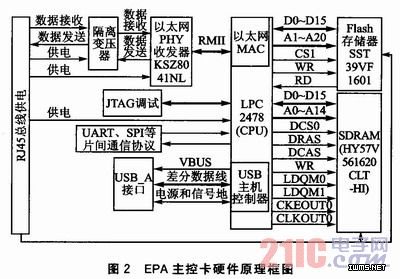

USB模块由CPU内部集成的USB主机控制器和外围电路构成,实现USB设备的热插拔、即插即用以及信息交换;总线供电模块RJ45接口在提供数据通信的同时还为现场设备提供总线供电;存储模块主要作为程序存储空间和内存。结合CPU特性,以太网PHY收发器采用RMII连接,存储模块通过总线连接。

2.1 ARM微处理器

CPU选用基于ARM7TDMI—S核的微处理器LPC2478,其运行频率高达72 MHz,具有高性能的32位RISC结构、16位的指令集,具有低功耗等特点。它的内部资源丰富,包括1个10/100M以太网媒体访问控制器(MAC)、1个带4 KB终端RAM的USB全速设备/主机/OTG控制器、4个U1AR-T、1个SPI接口、512KB片上Flash程序存储器。同时还带有1个4 MHz的片内振荡器、98 KB RAM(包括64 KB局部SRAM、16 KB以太网SRAM)以及1个外部存储器控制器(EMC)来支持上述的各种串行通信接口。这些特性使得它非常适用于通信网关和协议转换器,为多种类型的通信应用提供了理想的解决方案。

2.2 以太网PHY收发器

KSZ8041NL是MICrel公司推出的第6代PHY(局域网接口)解决方案。它具有功耗低、体积小、波形稳定、价格便宜等特点。该芯片拥有150 mW的低电耗,以及6kV的针对快速以太网收发器的高静电放电(EleCTRo Static Discharge,ESD)保护功能。

2.3 存储模块

外部存储器采用美国SST公司的SST39VF1601。这是一个1M×16位的CMOS多功能Flash(MPF)器件,尤其适用于要求程序、配置或数据存储器方便和低成本的应用。对于所有的系统,SST39VF1601可以显著增强系统的性能和可靠性,降低功耗。

内存芯片(RAM)HY57V561620CLT—HI是一个32MB、16位的CMOS同步DRAM,它用于高带宽大容量的主存储器。HY57V561620CLT—HI的运行与时钟的高电平同步,所有数据的输入和输出都与输入时钟的上升沿相同步。数据通过内部的管道来达到非常高的数据带宽。所有的输入和输出电压电平都和LVTTL电平相匹配。