D/A转换器用的芯片是AD5424,该芯片为电流输出型,8位的分辨率,17ns写周期,DAC转换时间是30ns。FPGA接收到控制模块的命令后从RAM中给D/A不断的发送8位的二进制数据,芯片通过自身内部一定的电路把前面发送的二进制数据转换成相应的电流,发送数据的时间是通过该芯片的技术资料中的时序图来控制的,每一个CS的写周期是t3+t7=19ns,中间转化是t7+t8=29ns。当再来一个有效信号时数据就被读出,当写信号有效时又开始写入新的数据从而往复循环。

从AD5424输出的电流通过下拉电阻转换成电压,经过第一个运放使电压跟随起到加强信号的作用,假设输出的电压是VLF353,通过第二个运放实现放大,第二个电路实际是一个负反馈的电路,通过公式

可得把VLF353放大了两倍,最后实现输出,从而完成了从D/A到调理信号,再到输出这一过程。

转化后的电压需要4路同时输出,一共有四种信号,所以采用ADG706这款芯片实现16路信号选择。FPGA给ADG706发送命令控制什么时间选择哪一路开关导通。每一个从模拟开关出来的电压都需要通过滤波器模块,这里用到的是OPA4340这款芯片,同时在每一个输出后面加入一个电容以便保证电压连续输出。

在整个系统中每一个芯片都需要电源的供电,而每个芯片所需要的电压也不一样,根据需要电源模块从外界引入一个5 V的电压通过TPS70358芯片转换成3.3V和2.5V,通过SPX3819M5-L-1-5芯片把5 V转化成1.5V。

3 软件设计

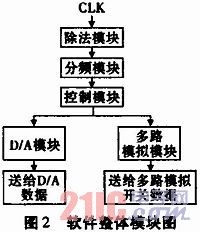

这个软件的整体设计如图2所示,主要分为五大模块:除法模块、分频模块、控制模块、D/A模块和多路模拟模块这五部分。每一个模块都有一定的功能,是一级一级实现的,软件的整体功能是达到波形的多路输出,频率可调的功能。

由于芯片的限制,在该芯片中写入的程序时不能有除法运算,但是在这里为了选择频率必须用到除法,所以在写入程序前先写入一个除法程序模块;由于要输出的是多路信号,为了实现这一设计要求通过控制D/A和多路模拟开关两个芯片的时钟,使得他们在时钟上不同步,D/A输出的模拟信号在四个输出口都可以输出,由于肉眼识别的时间差异可以达到四路同时输出这一效果。在图3中LOAD是除法模块中的使能端高电平有效,B[8..0]是控制频率的,SWITCH[1..0]是选择输出波形的,这三个都是输入端,输出端是两个,ADGDATA[3..0]和DATA[7..0],前面是多路模拟开关的输出信号,后面是DA的输出信号,从图中可以看出DA输出一个信号的时候多路模拟开关不断的在四个开关口选通。

上一页 [1] [2] [3] 下一页