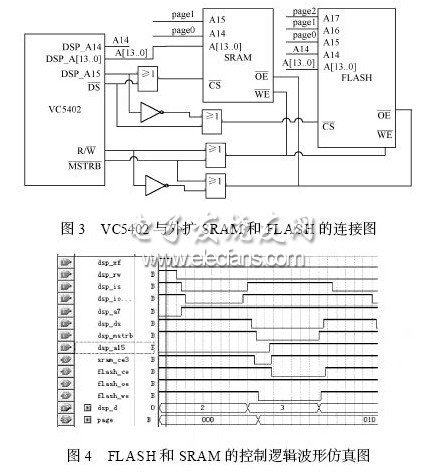

对FLASH 空间的某一地址进行访问时,应分为以下几步:

首先,解析该地址,进行地址分割,低15 位为页内地址,高3 位作为页选择地址;

其次,把页选择地址用PORTW 命令送到所分配的I/ O空间PA 中,等选通信号使能后,页地址就在所选存储器的高端地址线上;

最后,使用访问数据的指令。由于VC5402 的数据是16 位的,因此在调用数据指令时,需要16 位的数据。这里,低15 位来自所要访问的地址的低15 位,最高位补零。

要对Flash 存储器的高端进行访问,必须先对CPLD送数。如要寻址70000 H 存储单元时,假定AR3 辅助寄存器指向某一存储单元,CPLD 映射在VC5402 I/ O 空间的地址为PA ,其大致操作如下:

ST # 07H , *AR3

PORTW * AR3 ,PA

这样,CPLD 充当的锁存器将111 这3 位数给锁存住,在选通FLASH 时,将数据111 送至FLASH 的A15~A17端,然后再对DSP 存储器的地址0000 H 进行读写操作即可。

DSP 的扩展I/ O 端口

VC5402 仅有这2 个通用I/ O 引脚往往是不够的,DSP 为了一些特殊的需要提供了多个片上设备,比如3 个多功能串口、HPI 接口等。这些片上设备在系统中并没有用上,因此可以利用DSP 的扩展功能将这些设备的管脚扩展为通用I/ O 端口供系统使用。比如将HPI 端口的8 位并行数据线扩展为8 位I/ O 端口,用来和CPLD 进行通信,这些I/ O 口的扩展是通过对DSP 的相关寄存器进行相应的设置来实现的。

为了实现DSP 和CPLD 之间的交互,将HPI 的数据线用作通用I/ O 端口实现了VC5402 I/ O 口的扩展。HPI数据线扩展为通用I/ O 口的具体方法:在HPI 接口不允许,即在复位时HPIENA 引脚为低电平的情况下,使用2 个存储器映射寄存器(通用I/ O 控制寄存器GPIOCR 和通用I/ O 状态寄存器GPIOSR) 来控制HPI 数据引脚的输入输出。GPIOCR 和GPIOSR 在DSP 的物理地址分别是003CH 和003DH。

如要从扩展的HPI 口输出数据40 H ,需要进行以下3 步操作:

第一步:在复位时,将HPIENA 引脚置为低电平;

第二步:将通用I/ O 控制寄存器GPIOCR 的值设置为0x00FF ;

第三步:将通用I/ O 状态寄存器GPIOSR 的相应位设置为01000000 ,即40 H。

实现的程序代码如下:

STM # 0x003C ,AR3 ; 选中控制寄存器

ST # 0x00FF , *AR3 ; 将HPI数据端置为输出状态

STM # 0x003D ,AR3 ; 选中状态寄存器

ST # 0x0040 , *AR3 ; 输出数据40H

结 语

利用CPLD 实现VC5402 的存储器空间扩展,大大简化了硬件电路的设计,编程灵活;调试时,只需对CPLD 电路进行调试,简单方便,此方案可以推广到其他便携式图像采集处理系统的存储器扩展中。