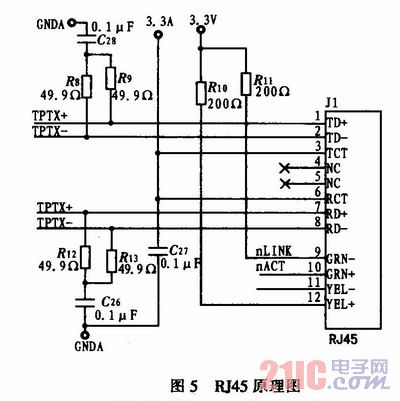

2)RJ45电路图5为RJ45的参考原理图,RJ45插座的4根两对差分信号线(TPTX+、TPTX-、TPRX+和TPRX-)分别连接到W7100的对应引脚(TXO-P、TXON、RXIP和RXIN)。在布线时需要特别注意的是:每对差分信号线之间尽量平行、靠近且长度相等,这样做是为了减少信号干扰。

3)CH341T电路 CH341T通过串行口RXD、TXD与W7100相连。在9和10脚需要连接12 MHz的晶振。8脚(UD-)接USB插座的2脚,7脚(UD+)接USB插座的3脚。USB插座的1脚接5 V电源,4脚接地。

4)X5043的连接 由于在W7100下载程序的时候不能受到X5043的影响,所以必须要在其与nRST引脚上添加一个跳线。在下载程序的时候要拔掉跳线帽,等下载完成之后再接上。要使X5043在上电之后开始工作必须在nCS引脚有一个从高电平到低电平的下拉。另外由于必须要与手动复位按钮共用nRST信号线,所以在复位键旁边不能并联大电容,这样会将复位信号过滤掉。

5)电源设计 由于W7100芯片集成了以太网物理层,因此在布线时存在数字电源与模拟电源、数字地与模拟地的混合设计。总共包括1.8 V、1.8 D、1.8 A、3.3 V、3.3 D、3.3 A、数字地GND和模拟地GNDA,它们分别连接到W7100和其它器件的对应引脚。印刷板的铺地是数字地,但是模拟地也要尽量的宽。1.8 V、1.8 D和1.8 A之间用1μH电感相连接,同样3.3 V、3.3 D和3.3 A之间用1μH电感相连接,每种电源和地之间用一个10 μF的电容相连接。

6)W7100引脚连接 W7100的XTLN0和XTLP0为内部PHY的晶体的输入输出。使用25 MHz平行共鸣晶体连接到这两个端口,以稳定内部振荡器。同样XTLN1和XTLP1引脚为W7100内核的晶体输入输出端,使用11.059 2 MHz平行共鸣晶体连接到这两个端口。

TM3-0和PM2-0引脚悬空,采用默认模式。BOOTEN引脚为启动代码控制,低电平运行应用程序代码,高电平运行下载程序,所以必须使用跳线方式将其分别连接到地和高电平,在开机时通过跳线进入不同运行状态。

F64EN引脚要外接4.7 k下拉电阻。RESETBG为PHY片外电阻,需要连接一个12.3 k(误差在1%以内)的电阻到地。RXLED和TXLED分别通过两个二极管连接到网口的nACT引脚(nACT需要上拉4.7 k电阻),用来指示数据传输。

nINT3引脚和LINKLED引脚共同连接到网口的nLINK引脚,用来驱动连接指示灯。

7)实物参考图 以上6点就是读卡器的几个重要部件的设计参考,在实际应用中可根据性能需要采用更加成熟的模块,这样会获得更好的效果。如在某工程中对刷卡可靠性要求很高,采用了周立功单片机公司的ZLG500AT模块作为刷卡模块。读卡器主板如图6所示。