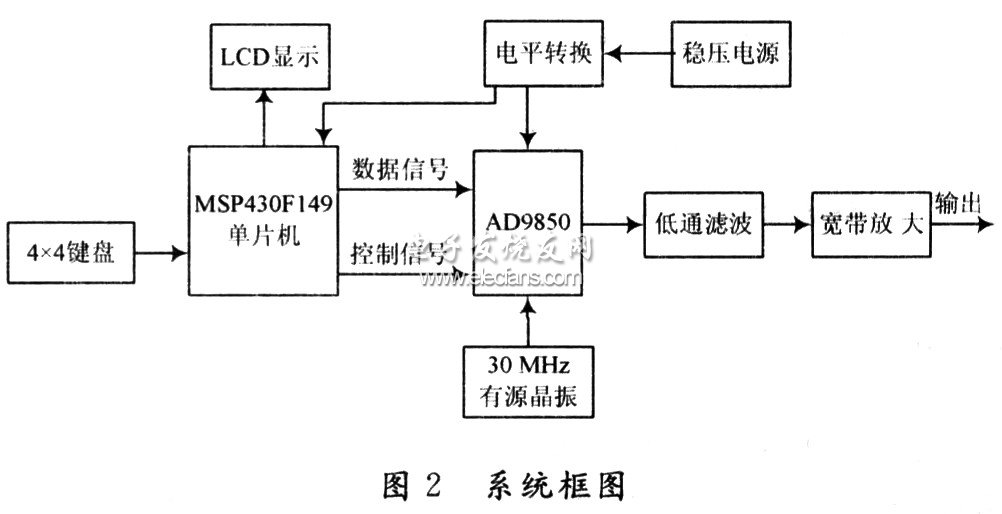

该系统采用MSP430F149对DDS进行控制构成方波正弦波信号源的系统框图如图2所示。

该信号源由MSP430F149单片机、DDS芯片AD9850、低通滤波器(LPF)、4×4软键盘、1602液晶显示屏和外部参考时钟源、宽带放大器和稳压电源等组成。其中,低通滤波器是信号源中的关键器件,负责滤除正弦输出信号中的高频、杂散信号和谐波信号;稳压电源的+5 V电压经过电平转换后为MSP430和AD9850提供+3.3 V的电源电压;外部参考时钟源选用30 MHz有源晶振,MSP430F149与AD9850采用串行通信方式连接。

1.3 硬件设计

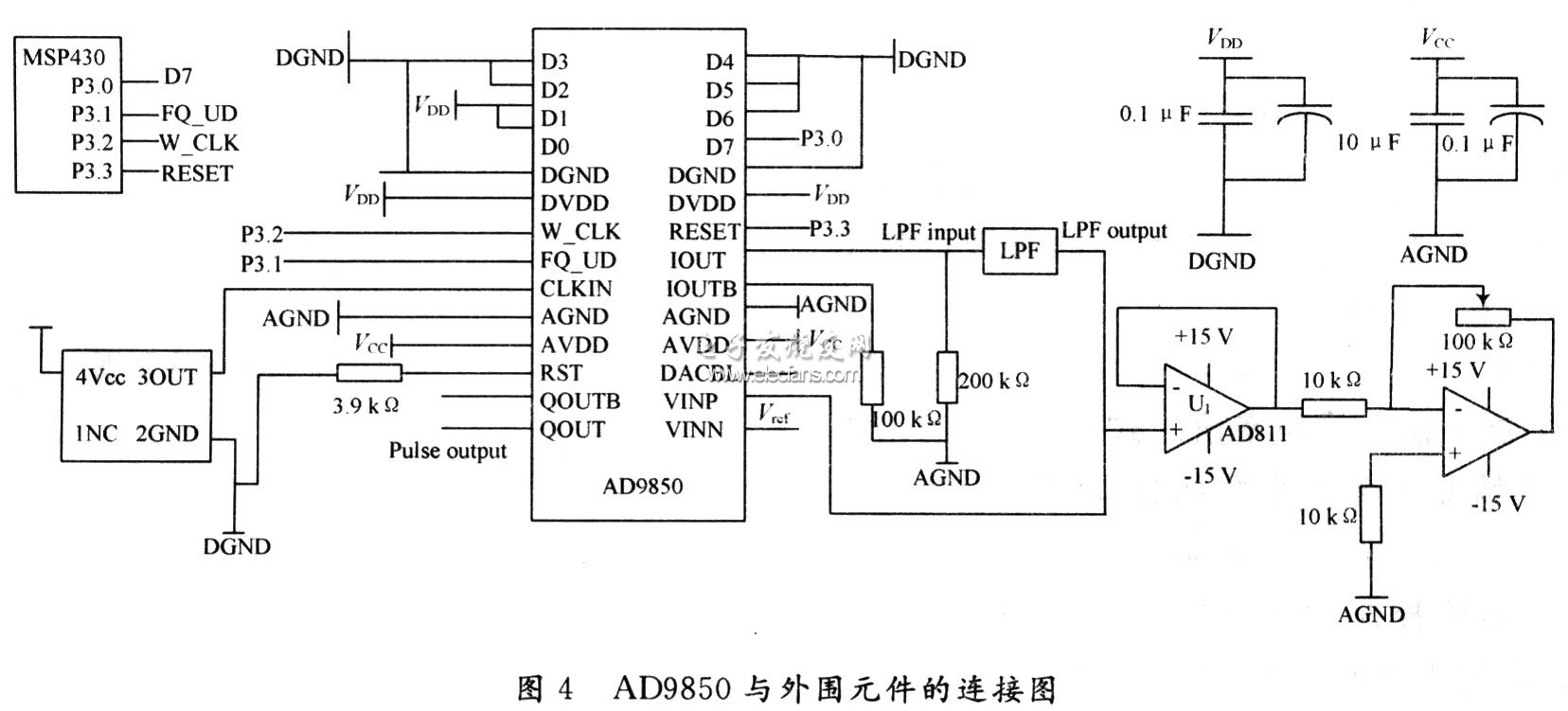

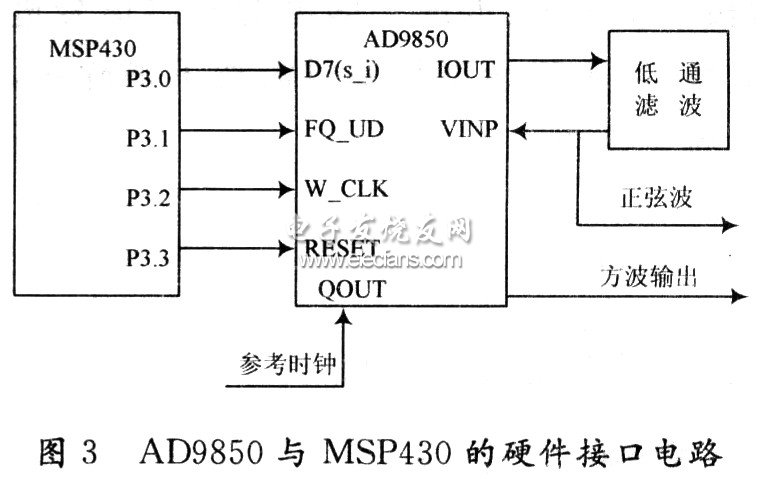

该信号源选用MSP430F149作为核心控制器,为了节省I/O资源,方便系统功能扩展,MSP430与DDS芯片AD9850之间采用串行通信方式,接口电路如图3所示。AD9850与外围元件的硬件连接图如图4所示,AD9851的正弦输出信号端IOUT接至外部的低通滤波器,滤除高频杂散和谐波后,一路信号经过宽大放大器AD811放大后输出需要的正弦信号,另一路再回接到AD9851内部比较器的正向输入端(VINP)以得到方波信号。其中:DGND为数字地;AGND为模拟地;VCC为模拟部分的电源电压;VDD为数字部分的电源电压。D7,FQ_UD,W_CLK,RESET分别接至MSP430的P3.0,P3.1,P3.2,P3.3上。为降低噪声信号对放大器的影响,在低通滤波器与宽带放大器之间接一级高速电压跟随器隔离,AD9850的输出信号峰峰值为1~2 V,为增大AD9850输出信号幅值,采用单位增益带宽为140 MHz,Sr=2 500 V/μs的高速宽频带运放AD811进行信号放大,并且通过调节反馈电阻来改变增益,从而调节输出信号幅度。放大电路的最大放大倍数,可以满足一般的应用需求。

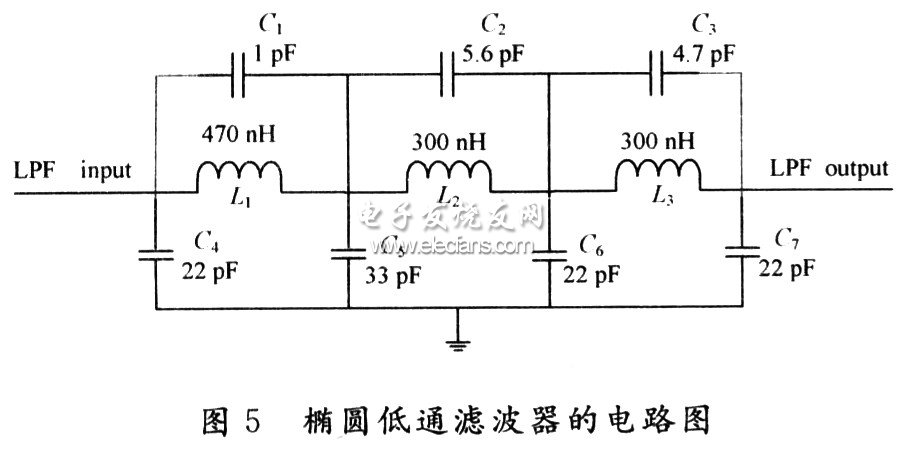

1.4 低通滤波器设计

低通滤波器是直接数字频率合成器的重要组成部分,其性能的优劣直接影响整个直接数字合成器的特性。在整个DDS实现过程中,低通滤波器除了滤掉高频信号之外,还有除去杂散的作用。DDS的杂散主要来源以下三个方面:

(1)ROM幅度量化误差:相位转化为幅度,是通过寻址ROM实现的,然而ROM地址中存有的波形幅度值字长是有限的,ROM存储能力有限而引起的舍位误差就是幅度量化误差;

(2)相位截断误差:为了提高DDS的精度,DDS的相位累加器位数都取得非常大,但ROM的容量是有限的,因此只利用相位累加器的高M位ROM寻址,其低(N-M)位被截断。由此引入的截断误差是DDS杂散的主要来源;

(3)DAC的转换误差,即DAC中非线性引起的转换误差:DAC有限的分辨率、非线性特性以及转换过程中出现的尖峰脉冲均会导致频谱质量变坏。因此,低通滤波器的使用是非常必要的,其性能的优劣直接关系到整个DDS的技术指标。

低通滤波器可以分为巴特沃什滤波、切比雪夫滤波、贝赛尔滤波和椭圆滤波等。巴特沃什低通滤波器通带和阻带都是平坦的,但是其过渡带太过平缓;切比雪夫低通滤波器的通带是等波纹抖动的,阻带是平坦的,过渡带比巴特沃什稍陡;贝赛尔低通滤波器和切比雪夫低通刚好相反,通带平坦,阻带是等波纹抖动的;椭圆低通滤波器的通带和阻带都是抖动的。但是其过渡带下降迅速,过渡带很窄。在该系统中,为了使输出信号频率最高10 MHz时能够最低程度地降低AD9850外部系统时钟30 MHz的干扰,采用具有较窄过渡带特性的椭圆滤波器,并采用7阶椭圆低通滤波。根据系统要求,输出信号的频率可达10 MHz,设定其通带为10 MHz,且7阶滤波具有下降速度更快的过渡带,可以有效地滤除10 MHz以上的高频干扰。考虑到实际的椭圆滤波器设计与理论分析是有所不同的,在此使用Multisim 9经行仿真后得出椭圆滤波器的具体参数。椭圆低通滤波器的电路图如图5所示。