・上一文章:Cortex-M3的生态物联网数据采集分站设计

・下一文章:单片机的多段语音组合录放系统设计

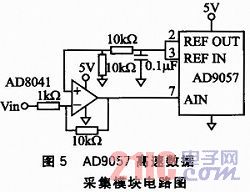

1.4 高速数据采集模块电路设计

AD9057是8位的模数转换器,可以达到60 MHz的最大采样频率。设计中,模块采用50 MHz的采样频率,AD9057带有2.5V的基准电压,可以对1 V峰峰值输入模拟信号进行A/D转换。通常采用高频、宽带运放对模拟信号进行缓冲,本设计中采用AD8041作为放大器,AD9057高速数据采集模块电路图电路图如图5所示。

2 结论

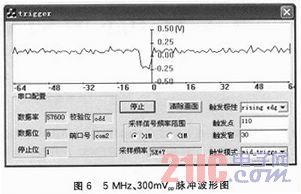

模块可以工作在50 MHz的采样频率下,并且在模拟信号幅度偏小和有一定干扰的情况下也可以正常地工作。本次设计中采用了VC++6.0编写的显示控制界面进行模块验证。图6是数据采集模块捕捉的频率为5 MHz、300mVpp交替出现间隔为1 ms的一个脉冲波形图。

其中,触发模式选用中间触发,触发极性为上升沿,采样频率为50 MHz。由此可见,本模块的技术方案可行,具有灵活简洁的特点,可以应用在程控仪器和自适应信号采集与处理系统中。