・上一文章:基于Android系统的H.264视频压缩技术实现

・下一文章:基于麦克风阵列的信号采集处理系统设计

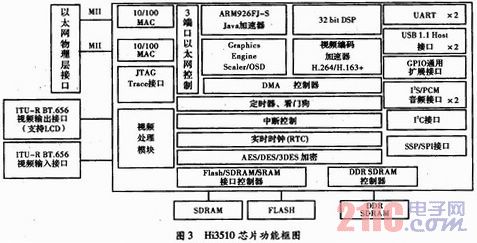

Hi3510采用高压缩比、低失真度的H.264编码方式和BP H 264算法,具有ARM926KJ-S、DSP双处理器内核以及硬件加速引擎的多核高集成度的SoC构架,视频处理功能强大。具有独立的16 kB指令Cache和16 kB数据Cache,内嵌16 kB指令紧耦合存储器和8 kB数据紧耦合存储器以及DSP增强结构,内嵌32×16 MAC和Java硬件加速器,内置MMU,支持多种开放式操作系统,最高工作主频可达240 MI·s-1,其功能结构如图3所示。

在使用SAA7111A前必须先对Hi3510中DSP的I2C控制模块进行初始化,通过SAA7111A上的I2C总线接口引脚(SDA)和引脚(SCL)来设定SAA711 1A寄存器的工作参数。I2C模块初始化结构如下: