����һ���£�MOS-FET���ص�·

����һ���£�����ά���������������Ͼ��䰸������

1�����ؿ��Ƶ�·

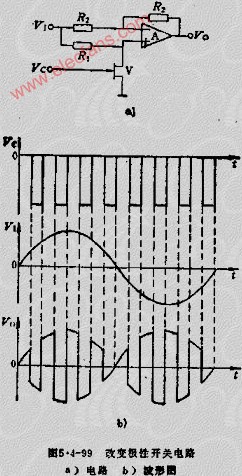

ͼ5.4-97Ϊ��J-FET���ص�·�������Ƶ�ѹVC���������ѹV1ʱ��VGS=0��J-FET��ͨ�������ź���VO����VC��V1�㹻����VD��ͨ��J-FET��ֹ��VO=0��

2���Ľ���J-FET���ص�·

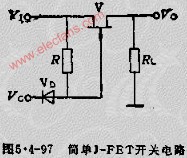

ͼ5.4-98��·��ͼ5.4-97��·�ĸĽ�������һ������Ŵ����Կ˷�J-FET����ϴ��ȱ�㡣��·��R1ʹJ-FET�ϵ�ѹ����С����VD��VS=0����VC=0ʱJ-FET��ͨ����V1��С�أ���VC�ȼжϵ�ѹ�Ը�ʱ��J-FET��ֹ������VD1��VD2��ͨ��©����λ��ǯ�ڡ�0.6V��R1����ֵ��V1�ķ�ֵѡ��������Ŵ����������źŵ��ࡣ

3���ı伫�Ե�J-FET���ص�·

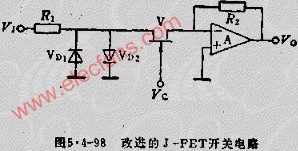

ͼ5.4-99A��ʾ��·Ϊ�ɸı伫�ԵķŴ��·����·ӦʹR1Զ����J-FET��ͨ�����ԶС��J-FET�Ľ�ֹ���裬��RON��R1��ROFF����©��Դ���ԣ�����VC=0ʱ��J-FET��ͨ����·Ϊ�����������VO=-V1����VC��V1��ͷ��Ȼ���ʱ��J-FET��ֹ��R1������������Ŵ���ͬ������˵�λFIN+=V1�����ڷ�������������˵�λVIN-=V1��R3������������V0=V1��R1��һ����R1��Ȼ�ƥ�䣬�������Ŵ��������迹�ܸߣ�R1��ѡ��Щ��ͼ5.4-99Bʾ����һ��ͨ���õ�·���źŲ��Ρ�