4 数字锁相式频率源硬件和软件调试

在完成频率源的软硬件设计之后。需要进行系统调试。调试包括硬件调试和软件调试两部分。

4.1 系统硬件调试

在完成系统硬件电路设计和PCB制作后,需要利用万用表、示波器、频谱仪等工具对系统进行调试,来验证设计是否达到系统设计的要求,有无电路方面错误等。硬件调试主要包括数字锁相环调试,上电前检测、上电后检测和模块各组成部分工作状态调试等。

在设计中,通过USB-Blaster下载电缆采用JTAG配置方式将数据下载到FPGA。下载配置是验证系统中其他电路部分的第一步,方法是通过QutartusⅡ软件设计一些简单的逻辑电路,然后下载到FPGA中,通过示波器等工具检测输出的波形是否正确。

4.2 系统软件调试

该设计中,在FPGA内用AHDL硬件编程语言实现了软件设计部分,主要分为两部分:一是对ADF4111寄存器的配置;二是实现按键对锁相频率升高和降低的要求。该设计中,利用数字示波器的触发采样功能来捕获FPGA配置ADF4111寄存器的各个管脚的时序逻辑。

ADF4111需要配置的寄存器为3个24 b的寄存器,在Altera公司的QuartusⅡ平台上用AHDL进行编程配置的仿真时序如图6所示。其中,R=40,A=6,B=8,P=8。

ADF4111有一个复用输出管脚(muxout),通过该管脚可以查看寄存器配置是否正确。设计中设置该引脚输出为PLl锁定指示,并连接到发光二极管。配置完后,若指示灯亮,则说明配置正确,PLL锁定在输入时钟上。调试中配置完ADF4111后,PLL成功锁定设置的频率上。

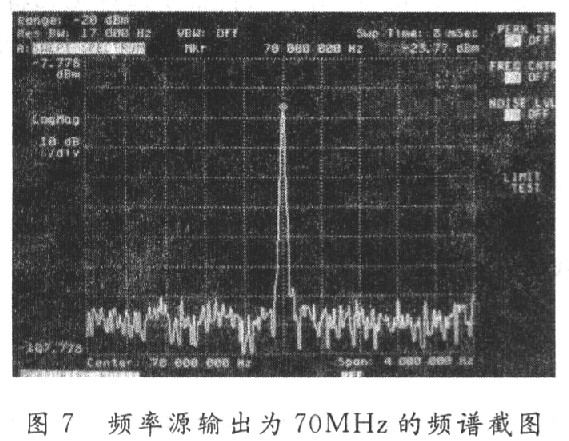

在整个设计和调试完成之后,用频谱仪对数字锁相式频率源输出频率进行了测试,图7为70 MHz输出时的频谱图,可以看出,频率源输出稳定。需要注意的是,截图显示的本振输出功率为-23.77 dBm,这是由于对本振输出进行测量时采用的探头有损耗,经测量约有33 dB的损耗,故本振输出的实际功率为9 dBm,达到系统设计要求。

5 结语

本文采用FPGA与频率综合器ADF4111相结合的方法进行了数字锁相式频率源的设计,在FPGA内用AHDL硬件描述语言编写频率综合器需要的频率控制字程序,产生范围为70~90 MHz的高精度频率,频率的步进采用按键控制的方法,步进的间隔为1 MHz,并通过数码显示管将锁定后的频率值显示出来。完成了PCB板制作,进行了硬件和软件调试。通过ADF4111的复用输出管脚(Muxout)看到PLL成功锁定设置的频率上,并用频谱仪测量了产生的频率,输出频率稳定,精度高,功率符合设计指标要求。实现了PLL输出频率的步进,间隔为1 MHz。并在数码管上将锁定后的频率值显示出来。

在该系统中,由于ADF4111的控制字寄存器的控制字是通过FPGA写入的。所以可以通过软件设计的方法,改变写入的控制字来实现不同频率的本振信号输出,使锁相环具有低相位噪声,低杂散度。快速锁定的特点,电路简单,易于调试。采用这种方法能可根据实际工程需要改变输出信号的频率。步进间隔以及功率,使该类型电路设计能广泛应用于无线通信设备中,为设备的中频和射频电路提供高质量的本振。