・上一文章:基于GPRS的嵌入式系统远程监控和升级

・下一文章:采用可编程逻辑器件和A/D转换器的高速数据采集卡的设计方案

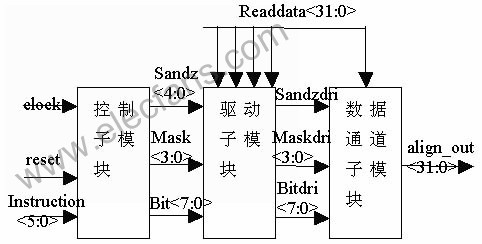

以上是Load Aligner模块数据通道部分的设计。它还需要有控制模块来产生上述控制信号,此外由于任何一个控制信号都要驱动数据通道子模块中的32个cell,所以还要有一个驱动模块来使控制信号有足够的驱动能力。由以上分析,整个Load Aligner模块的框图如图2所示。其中,控制模块采用自动布局布线生成,而驱动模块和数据通道模块均采用全定制设计。

功能验证

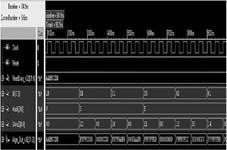

对此模块的RTL代码和所设计的电路分别进行了功能验证。设从DCACHE取出的32位数据用十六进制表示为AABBCCDD,对表3中的所有指令进行测试。图3所示的波形图就是依次测试指令LW、LH00、LHU00、LH10、LHU10、LB00、LBU00、LB01、LBU01、LB10等的结果。可以看出,结果与表3完全吻合。说明所设计的电路满足设计目标,可以实现所要求的所有指令。

电路仿真

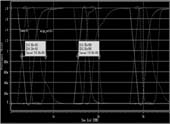

根据图1可以看出,从符号选择信号Sandz<4:0>到输出的路径为最长路径,我们选取这条路径进行仿真,并考虑在0.18μm时线电阻电容对时延的影响,用Hspice确定了所需器件的尺寸。仿真结果如图4所示。上升时时延为0.52ns,下降时时延为0.47ns,均满足小于0.7ns 的要求。

结论

在CPU中,Load Aligner模块是DCACHE和数据通道之间的接口。从DCACHE中取出的数据只有通过Load Aligner模块重新排序,才能进入CPU的数据通道。在设计中应用了自上而下的设计方法,所设计的电路实现了所有的指令,在时延上也达到了设计目标。