设计目标

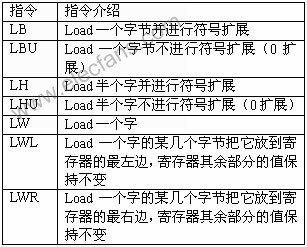

本设计中,Load Aligner模块要实现的指令有LB、LBU、LH、LHU、LW、LWL、LWR。CPU通过这些指令把从数据存储器中取出来的数据重新排序,然后放进寄存器堆RF中,进入CPU的数据通道。表1是对这些指令的介绍。

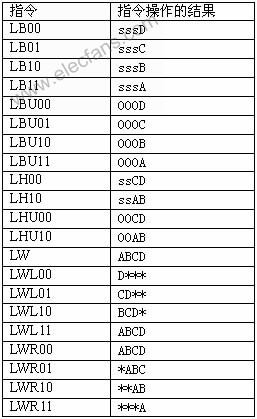

如果把从DCACHE中取出的一个32位的字表示成4字节:A、B、C、D,如表2所示。

31-24/ 23-16/ 15-18/ 7-0

A / B / C / D

那么经过上述指令操作后,这个字被重新排列的结果(即Load Aligner模块的输出,也用4字节来表示)见表3。

表3中,s表示符号扩展,*表示这个字节上的寄存器中的数保持不变。不过在Load Aligner模块,先将这些字节置0,在寄存器堆模块再控制这些字节是否直接写进寄存器。

以上是Load Aligner模块要实现的指令目标,另外由于此模块是CPU关键路径的一部分,因此数据通道部分最长时延不能超过0.7ns。

逻辑设计

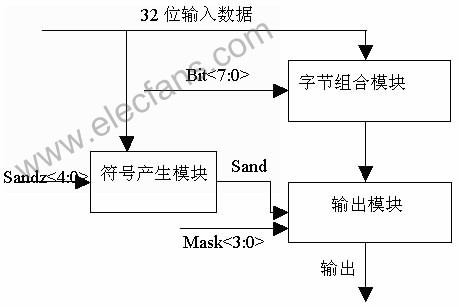

分析比较经过上述指令后Load Aligner模块的输入输出变化可以看出:输入字的每一字节经过Load Aligner模块后可以在输出字的任意字节位置上。换言之,输出字的每一字节都可以有A、B、C、D四种情况。所以需要一个8位的控制信号Bit<7:0>来控制四个四选一的数据选择器,称为字节组合模块,来获得所需要的字节组合。不过,经过这个字节组合模块选出来的4字节并不全是所需要的,还需要去掉冗余的字节或者进行符号扩展。因此需要有能够产生符号扩展或者0扩展的模块称为符号产生模块,然后把它的输出和一个4位的控制信号Mask<3:0>一起控制一组二选一数据选择器,称为输出模块,来获得最后的排序结果。逻辑实现流程图见图1。