・上一文章:带DSP功能的超低功率音频编解码器帮助解决音频方案挑战

・下一文章:基于富士通高清芯片的软硬件分离通用机顶盒设计

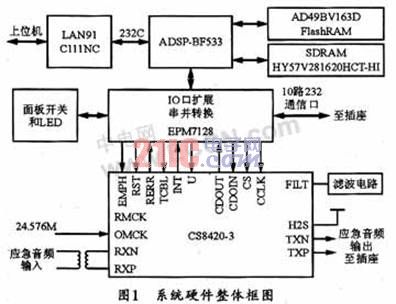

2 系统硬件设计

该系统设计是以ADSP-BF533为核心的音频信号处理系统,其主要硬件单元有ADSP-BF533、flash、SDRAM、总线接口、以及电源、时钟、JTAG调制器。此外还有CPLD芯片辅助处理。该系统的电源模块选用TPS70302,外围设备有不同的RC值,以构成不同的电压,这里需要产生3.3V和1.2V两种电压,此外,还有JTAG调试端口。整个处理器系统的硬件框图如图1所示。

2.1 SDRAM存储器

SDRAM存储器选用HY57V281620,其存储容量为4×2 Mx16位(16MB),工作电压为3.3 V,具有16位数据宽度,可以满足存储要求。HY57V281620的时钟由DSP的系统时钟提供。数据总线D[15:0]连接到DSP的16位数据总线。其接口电路连接如图2所示。

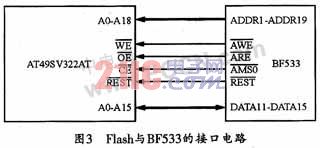

2.2 外部FLASH

由于BF-533内部的存储容量有限,因此必须外接FLASH以用于存储程序,FLASH芯片可选用AT49BV322AT,每次上电复位后,BF-533首先将FLASH中的程序引导到内核中,其电路连接如图3所示。

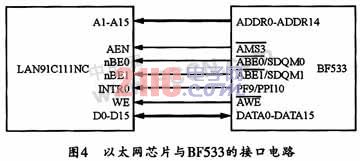

2.3 以太网芯片LAN91C111

由于LAN91C111是按通用标准时序设计的高速芯片,又是专为嵌入式系统设计的,因此,其外围电路相对比较简单。图4所示是LAN91C111与BF533的接口电路,图中,BF533的地址总线ADDR0~ADDR14与LAN91C111和A1~A15相连。A0没有被LAN91C111使用而悬空;数据总线则与D0~D15相连,用于16位数据传输。LAN91C111端的D16~D32悬空;LAN91C111的片选信号AEN由DSP提供。