摘要:针对SPI总线接口缺乏标准协议的特点,提出了SPI器件之间通信的一般方法。论文阐述了ARM芯片内置SPI硬件控制器的工作原理和时序,并对射频芯片TRF7960x的工作模式与读写要求进行了分析。在此基础上,根据TRF796x的时序特性和访问要求,采用ARM芯片的硬件 SPI方式实现对TRF796x的读写访问与控制,并在RFID门禁系统中验证了通信结果。

关键词:SPI;ARM;TRF796x;时序

引言

SPI(同步串行外围接口)是由Motorola公司最早提出的,出现在其M68系列单片机中。它是一种全双工的同步串行接口,采用主一从模式架构,支持多Slave模式应用,但一般仅支持单Master。由于其简单实用,又不牵涉到专利问题,因此许多厂家的设备都支持该接口,被广泛应用于外设控制领域。 SPI接口是一种事实标准,并没有标准协议,大部分厂家都是参照Motorola公司的SPI接口定义来设计的。正因为没有确切的标准协议,不同厂家的 SPI器件接口在技术上存在着一定的差异,有的甚至无法直接互连。本文对SPI器件通信时容易忽略的问题进行了分析。

1 S3C2440A内置SPI接口与工作时序

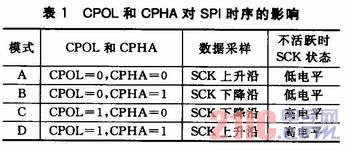

S3C2440A是Samsung公司生产的ARM9内核芯片,该芯片内置了2个SPI硬件控制器,大大简化了与SPI器件的通信。从 Samsung公司提供的Datasheet中可以看出,其内置硬件SPI结构主要由4部分构成:时钟分频器、8位发送移位寄存器、8位接收移位寄存器、控制逻辑等。其与SPI接口相关的寄存器包括控制寄存器(SPCONn)、状态寄存器(SPSTAn)、引脚控制寄存器(SPPINn)、预分频寄存器 (SPPREn)、发送数据寄存器(SPTDATn)、接收数据寄存器(SPRDATn,n=0,1)。其SPI接口共有4根信号线,分别是从设备选择线(SS)、时钟线(SCK)、串行输出数据线(MO-SI)、串行输入数据线(MISO)。当S3C2440A作为Master时,SS信号由S3C2440A驱动输出,用于选择激活某从 SPI器件,只有当SS信号线为低电平时,对应Slave设备的SPI接口才处于工作状态。为了满足不同SPI器件的通信特性,S3C2440A内置的 SPI接口定义了4种数据传输的工作时序,这4种时序是由控制寄存器(SPCONn)的时钟极性控制位(CPOL)和时钟相位控制位(CPHA)联合进行配置的。从表1可以看出,SPI的工作时序主要是根据数据采样的时刻(上升沿或下降沿),以及在没有数据传输时SCK信号所保持的状态来划分模式的。

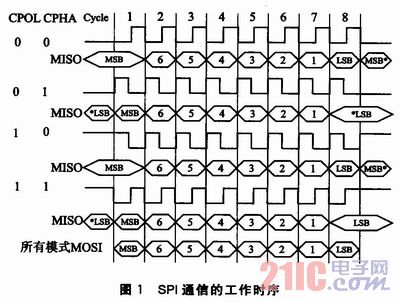

根据CPOL和CPHA设置的不同,S3C2440A内置SPI接口的4种工作时序如图1所示。需要注意的是,SPI通信的数据传输是以字节为单位进行的,且高位在前,低位在后,图1中的*LSB表示上一个传输字节的最低位,MSB*是指下一个传输字节的最高位。