引言

Nios II 处理器是Altera公司设计的一款基于FPGA的32位RISC嵌入式软核处理器,具有32位指令集、数据通路及地址空间,是其可编程系统芯片(SOPC)的核心。Nios II系统采用Altera公司设计的一套Avalon总线交换结构,Avalon总线上的所有信号都与系统时钟同步且地址、数据和控制信号使用独立的端口;支持各种传输方式;采用从端口仲裁机制,对于有多个主设备的系统可以提高系统的吞吐量。

采用基于FPGA 的Nios II软核处理器很容易在嵌入式系统设计中实现多处理器系统。在这样的多处理器系统中,一般外部处理器做主处理器,Nios II处理器为从处理器,两个处理器有共用的存储器可以进行数据交互。本文将通过对Nios II系统启动的研究设计一方案,用外部处理器配置FPGA,加载程序代码到Nios II系统中的程序存储器中,最终完成Nios II系统的启动。

在多处理器系统的启动方案

在多处理器系统中,为了降低成本,可以省去Nios II的一个非易失性存储器外设,如flash、EPROM等,Nios II处理器通过Avalon交换结构连接易失性存储器,一个外部主处理器及一些必要的接口外设。因此延迟Nios II的启动是必要的,解决办法是在Nios II系统中设计一启动延迟模块,把此模块的基址设为Nios II的复位地址。通过此模块,Nios II处理器上电复位后启动被延迟,直到数据被传输完毕,外部处理器通过启动延迟模块向Nios II发送一个可以开始进入程序存储器的指令,然后跳转到程序存储器开始执行,完成后续的设备初始化及应用程序的执行。

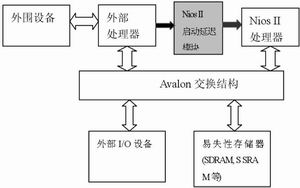

外部处理器通过时序转接桥连接在Avalon交换结构上和Nios II处理器共同构成的一个双处理器系统如图1所示。黑色箭头表示Nios II启动延迟模块是通过Avalon交换结构连接的。

图1 多处理器系统的启动方案结构

启动方案的硬件设计

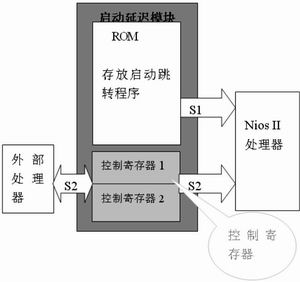

启动延迟模块如图2所示,它有两个从端口S1、S2:S1一端连接在启动延迟模块中的ROM单元上,另一端通过Avalon总线连接在Nios II处理器的指令主端口;S2一端连接在启动延迟模块的控制寄存器上,另一端通过Avalon总线连接在外部处理器和Nios II处理器的数据主端口。图2中箭头的方向表示数据的流向。

图2 Nios II启动模块的硬件结构