随着集成电路技术的高速发展,现代集成芯片的晶体管集成度和工作频率获得了较大提高,例如Intel处理器在一个内核中集成了上亿个晶体管,且工作频率已经超过2 GHz。目前,在器件水平上, CPU 散热器 的辐射发射已经成为一个主要的 电磁辐射 源。散热器上的能量主要由处理器里的硅核强耦合而来,另外还有散热器附近电路线的耦合。在GHz范围内,硅核的尺寸远小于时钟信号频率及其谐波的波长,所以硅核自身辐射很小,可忽略。但当能量耦合到散热器上情况就不同了,在这些频率上,散热器的尺寸相比于波长不能忽略。当散热器的固有频率接近于CPU的时钟信号频率时,散热器就表现出强辐射,很容易对周围环境产生电磁干扰,为了减少由此带来的干扰,必须要研究散热器的谐振特性及辐射特性。虽然无法精确模拟硅核中的电路以求解精确结果,但散热器的电磁特性随其相关参数(底面尺寸、鳍取向及高度)的变化趋势也非常重要。本文详细研究了散热器的底面尺寸长宽比、鳍的取向及高度对第一谐振频率(文中分析的均为第一谐振频率,以下简称谐振频率),及谐振频率点处电场增益及辐射方向的影响。通过研究,找出一般规律,为散热器的设计及选取提供依据。

1 数值模型建立

在EMC标准问题的研究中,CPU散热器问题是电磁兼容的主要问题之一。对于传统CPU散热器的建模,通常把散热器分解成3个部分:接地面、激励源和散热器。从实际集成电路的电磁特性来看,可以将CPU核的电磁特性模拟为一个导体贴片。Brench认为可以将散热器模拟为一个固体块以简化计算。Das和Roy通过实验结果得出结论,可以用单极子天线模拟激励源。

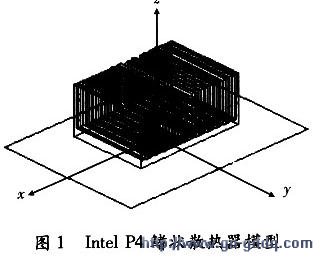

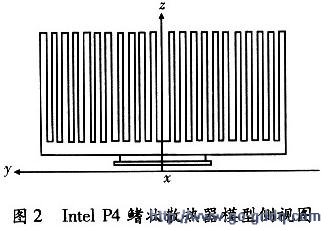

与传统的处理器相比,P4处理器的结构和封装有所不同:在集成芯片的顶部集成了一个散热片,并且和芯片的封装绝缘。因此,P4处理器与传统处理器的散热器数值模型有所不同,在文献中,将两种模型进行了对比,文献已经提出了一个简易多层结构数值模型。本文在P4多层简易数值模型的基础上,建立更加真实的鳍状散热器,如图1和图2所示。图2中由下向上,依次为接地板(Ground)、贴片(Patch)、介质(Substrate)、集成散热片(IHS)、散热器(HS)。在此模型基础上,详细分析了以下两点:(1)散热器底面长宽比的变化对谐振频点、谐振频率处电场增益及辐射方向的影响;(2)鳍的取向及高度变化对谐振频率、谐振频率处电场增益和辐射方向的影响。图1和图2中各部分的材料如表l所示。

2 仿真 分析

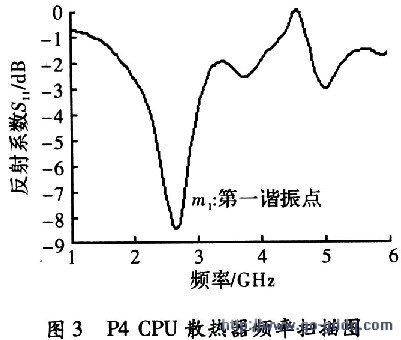

首先,将散热器看作一个固体块,采用标准尺寸88.9 mm×63.5 mm×38.1 mm,建立模型,对频率1~6 GHz进行扫频,得出反射系数,如图3所示。对比图3与文献中图4的结果可以看出,在第一谐振点基本一致,在低频处仿真结果更加准确。

2.1 散热器底面的长宽比对谐振频率、电场增益及辐射方向的影响

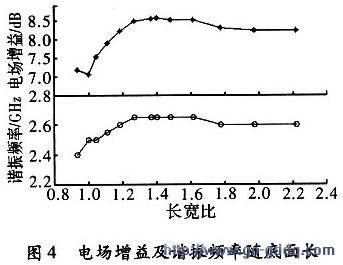

将散热器底面的长边及高度固定,变化宽边,观察谐振频率的变化和谐振频率处电场增益、辐射方向的变化。设定散热器长边为88.9 mm,高度为38.1 mm,宽边从40 mm变化到95 mm,每增加5 mm计算一次,即底面长宽比由0.93变化到2.22,得到电场增益及谐振频率随底面长宽比的变化图,如图4所示。

从图4中看出,(1)当长宽比>1.25时,谐振频率变化并不明显,保持在2.6~2.65 GHz。当长宽比减小时,谐振点将明显向低频偏移,例如,长宽比约为0.93时,谐振点已降到2.4 GHz。这是因为,当宽边<长边时,长边是优势尺寸,它决定了散热器谐振频率。当长边为88.9 mm时,它的谐振点在2.65 GHz左右,当宽边>88.9 mm后,此时宽边变为长边,成为优势尺寸,优势尺寸的变化主要影响了谐振点的变化。另外,在长宽比>1.65时,谐振频率有轻微下移;(2)当长宽比>1.3时,电场增益保持在8 dB以上,这个增益大于大多数无线通信系统中便携式器件的天线增益,散热器表现出天线效应。长宽比为1左右时,电场增益下降1 dB以上。另外,电场增益与谐振频率变化趋势基本一致。

图5给出了3个不同宽边尺寸时,CPU散热器电场增益二维辐射图(3=0),可以看出,辐射方向在θ=30左右。图6(a)~图6(c)给出了随宽边尺寸的增加,CPU散热器3维辐射图的变化。图6(a)是宽边为40 mm时的辐射图;图6(b)是宽边为60 mm时的辐射图;图6(c)是宽边等于长边为88.9 mm时的辐射图。由图6(a)到图6(c)的变化,可以看出随着宽边尺寸的增加,辐射方向由xz面的两个辐射方向渐渐变化为xz面和yz面4个辐射方向,这是因为长边对谐振点是优势尺寸,它主要影响了在谐振点处散热器的辐射方向特性。当宽边小于长边时,长边决定辐射特性,此时有两个辐射方向,如图6(a)和图6(b)所示;当宽边接近长边时,宽边将和长边一起决定辐射特性,此时出现4个辐射方向,如图6(c)所示。