����1 ����

���������źŴ������� DSP ���Ѿ���չ��20���꣬��������źŴ���������Ӧ�á��������� ���Ű뵼�弼���ķ�չ���������������ʹ�ܶิ�ӵĿ����㷨���ܵ���ʵ�֣�ͬʱ��ʵʱ���������Ϳ����������蹦�ܼ���һ�����ڿ���������Ҳ�õ��ܺõ�Ӧ�á����ֿ���ϵͳ�˷���ģ�����ϵͳ��·���ܵ�һ�����ƾ��Ȳ��ߵ�ȱ�㣬������������ǿ���ɿ��Ըߣ���ʵ�ָ��ӿ��ƣ���ǿ�˿��Ƶ�����ԡ�

���� TMS320LF2407A ������TI��˾�Ƴ�����������16λ���������źŴ���������ר��Ϊ���ֿ�����ƣ���DSP�ĸ����źŴ��������������ڿ��Ƶ��Ż���Χ��·��һ�壬�����ֿ���ϵͳ�е��Թ㷺Ӧ�� [1]�����Ľ�������ϵ�ṹ���������Լ����ڿ��������е�Ӧ�ã�Ϊ���ֿ���ϵͳ������ṩ�ο���

����2 ��ϵ�ṹ��������

����2.1 ϵͳ���

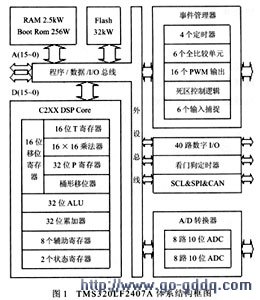

����TMS320LF2407Aϵͳ��ɰ�����40MHz��40MIPS�ĵ͵�ѹ3.3V��CPU��Ƭ�� �洢�� ���¼�������ģ�顢Ƭ�ڼ�����Χ�豸[2]������ϵ�ṹ��ͼ��ͼ1��ʾ��

����2.2 CPU�����߽ṹ

����TMS320LF2407A��CPU�ǻ���TMS320C2XX��16λ��������ںˡ���ϵ�ṹ�����ļ���ˮ�����ӿ�����ִ�У�����һ��������������ɳ˷����ӷ�����λ���㡣��������������Ԫ��CALU����һ��������������Ԫ��������һ��32λ��������Ԫ��ALU����һ��32λ�ۼ�����һ��16��16λ�˷�����MUL����һ��16λͰ����λ����ͬʱ�˷������ۼ����ڲ�������һ�������λ������ȫ������CALU�ĸ����Ĵ�����Ԫ��ARAU�������˸�16λ�����Ĵ���������Ҫ��������CALU������ͬʱִ�а˸������Ĵ�����AR7��AR0���ϵ��������㡣����״̬�Ĵ���ST0 ��ST1����ʵ��CPU����״̬�ı��档

����TMS320LF2407A������ǿ�Ĺ���ṹ��оƬ�ڲ���������16λ���ߣ��������ַ���ߣ�PAB�������ݶ���ַ���ߣ�DRAB��������д��ַ���ߣ�DWAB������������ߣ�PRDB�������ݶ����ߣ�DRDB��������д���ߣ�DWEB���������洢�����ߺ����ݴ洢�������������֧�ֲ��еij���Ͳ�����Ѱַ�����CPU�Ķ�/д����ͬһ�����ڽ��У����ָ�����������ʹ����Ӧ���ơ��������˲��������硢�Ŵ��㷨�ȸ��ӿ����㷨����ʵ�֡�

����2.3 �洢������

����TMS320LF2407A��ַӳ����֯Ϊ�����ɶ���ѡ��Ŀռ䣺����洢����64K�������ݴ洢����64K��������/�����I/O���ռ䣨64K������Щ�ռ��ṩ�˹�192K�ֵĵ�ַ��Χ��

������Ƭ�ڴ洢����Դ������544�֡�16λ��˫�˿�����/����DARAM��2K�֡�16λ�ĵ��˿�����/����SARAM��Ƭ��32K��16λ��Flash����洢����256�֡�16λƬ��Boot ROM��Ƭ��Flash/ROM���пɱ�̼������ԡ�

����TMS320LF2407A��ָ������ֻ����Ĵ洢��Ѱַ��ʽ������Ѱַ��ʽ��ֱ��Ѱַ��ʽ�����Ѱַ��ʽ��

����2.4 �¼�������ģ��

����TMS320LF2407A��������ר���ڵ�����Ƶ��¼�������ģ��EVA��EVB��ÿ���¼�������ģ�����ͨ�ö�ʱ����GP����ȫ�Ƚϵ�Ԫ���������������·�Լ�����Ԫ��

������ ͨ�ö�ʱ����TMS320LF2407A�����ĸ�16λͨ�ö�ʱ���������ڲ����������ڣ���Ϊȫ�Ƚϵ�Ԫ����PWM����Լ�������ʱ��ʱ����ͨ�ö�ʱ�������ֿ�ѡ��IJ���ģʽ��ֹͣ/����ģʽ������������ģʽ��������/������ģʽ��������/������ģʽ��ÿ��ͨ�ö�ʱ������һ����صıȽϼĴ���TxCMPR��һ��PWM�������T xPWM��ÿ��ͨ�ö�ʱ�������Զ�����������һ��PWM���ͨ�����ɲ����ǶԳƻ�Գ�PWM���Σ���ˣ��ĸ�ͨ�ö�ʱ�������ṩ4·PWM�����

������ ȫ�Ƚϵ�Ԫ��ÿ���¼�������ģ����3��ȫ�Ƚϵ�Ԫ��1��2��3��EVA���� 4��5��6��EVB������ÿ���Ƚϵ�Ԫ����һ�� 16λ�ȽϼĴ��� CMPRx����������CMP / PWM������ţ��ɲ���2· PWM����źſ��ƹ�����������������ż����ɿ��ƼĴ��� (ACTR)�Ŀ���λ��������������Ҫ��ѡ��ߵ�ƽ��͵�ƽ��Ϊ��ͨ�źţ�ͨ������T1Ϊ��ͬ������ʽ����ѡ������Գ�PWM���Ρ��ǶԳ�PWM���λ�ռ�ʸ��PWM���Ρ�

�����������Ƶ�Ԫ (DBTCON)���������ɱ�̵�����������ʹ����ÿ��ȫ�Ƚϵ�Ԫ����·CMP / PWM������ƵĹ��������ļ�ο������ڼ�û���ص������ɱ�̵���������ʱ���16��s��

������ �������������·�������������壨 QEP ����·���Զ�����CAP1/QEP1��CAP2/QEP2�ϵ���������������н���ͼ���������ֱ�Ӵ����������̵�2·�����������壬��������������������������У��б仯��Ƶ�ʺ��ķ�֮һ���ڣ�90�㣩�Ĺ̶���λƫ�ƣ��������2·�����źŽ��м����4��Ƶ��ͨ�����2·�źŵ���λ��ϵ�����жϵ������/��ת�����ݴ˶��źŽ��м�/���������Ӷ��õ���ǰ�ļ���ֵ�ͼ�����������Ľ�λ�ƺ�ת����Ľ��ٶȿ���ͨ�������Ƶ�ʲ����

������ ����Ԫ������Ԫ���ڲ��������������źŵ����䣬�����¼�������ģ���ܹ�����������Ԫ��EVAģ������������Ԫ����CAP1��CAP2��CAP3�����ǿ���ѡ��ͨ�ö�ʱ��1��2��Ϊʱ������CAP1��CAP2һ��Ҫѡ����ͬ�Ķ�ʱ����Ϊʱ����EVBģ��Ҳ����������Ԫ����CAP4�� CAP5��CAP6�����ǿ���ѡ��ͨ�ö�ʱ��3��4��Ϊʱ������CAP4��CAP5һ��Ҫѡ����ͬ�Ķ�ʱ����Ϊʱ����ÿ����Ԫ����һ��������FIFO�����ջ����������ʱ����Ӧ���жϱ�־����λ������CPU���ж�����