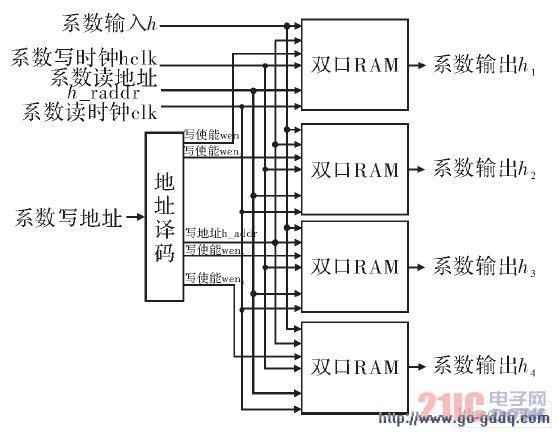

2.2 滤波器系数存储模块

滤波器系数存储模块和输入序列缓存模块相对应,采用双口RAM模块实现,共有4个256深度的双口RAM模块,如图3所示。

图3 滤波器系数存储模块实现框图

4个子块使用相同的输入数据线,通过系数写地址的译码,生成各子块的写使能’wen1~wen4和写地址h_addr,控制输入的系数按照顺序依次存入到RAM中。系数的读地址h_addr由控制模块生成,4个子块共用一个读地址,输出与数据相对应的系数h1~h4到乘累加模块,进行乘累加运算。

2.3 控制模块

控制模块产生输入序列缓存模块的读写地址、使能信号以及滤波系数存储模块的读地址、使能信号,并对乘累加运算进行控制。

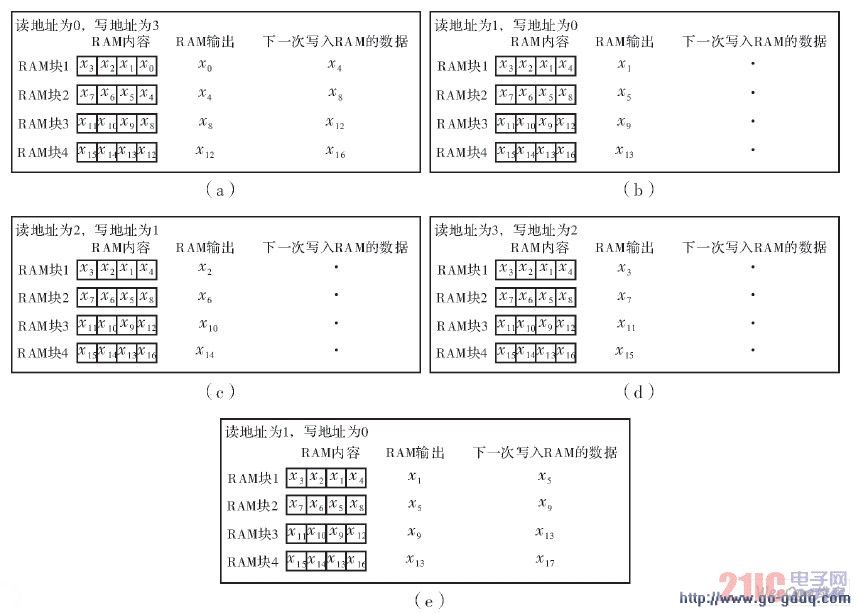

输入序列需要在缓存模块中反复移位输出进行运算,每256个时钟周期输入1个数,输入序列的写地址必须滞后读地址一个时钟周期,才能保证数据的连续、不丢失。这样新写入的数据不在固定的位置,就要求读地址也不是单纯的累加关系。以每个RAM块深度等于4为例研究读写地址的关系,如图4所示。

图4 每个RAM块深度为4时读写顺序

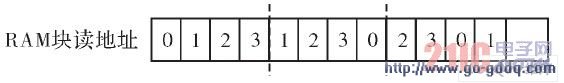

可见此时输入序列的读地址顺序如图5所示。

图5 每个RAM块深度为4时读地址

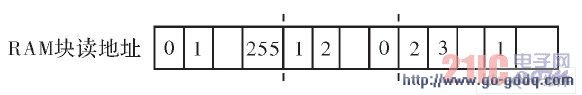

由此类推可得实际输入序列缓存模块的读地址如图6所示。

图6 输入序列缓存模块读地址

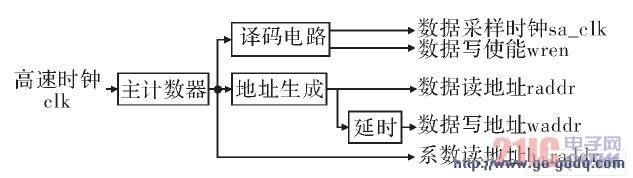

整个控制模块的实现如图7所示。主计数器整体计数,每256个时钟周期,地址产生模块就把计数器的计数值整体加1,作为输人序列的读地址raddr输出,实现了图6所示的地址顺序。写地址waddr由读地址raddr经延时一个时钟周期获得。由于输入序列是按时间顺序输出的,故滤波系数只要从存储阵列中也相应地顺序输出就可以了,将主计数器的计数值直接引出作为滤波系数阵列的读地址h_addr。

图7 整个控制模块的实现

主计数器的输出经过译码电路后,输出数据的低速采样时钟sa_clk,用来同步输入序列。还输出输入序列的写使能wren,每256个时钟周期使能一次,写一次数据。