・上一文章:基于反馈技术的宽带低噪声放大器的设计

・下一文章:基于V600ME14-LF的锁相环设计

2.4 乘累加模块

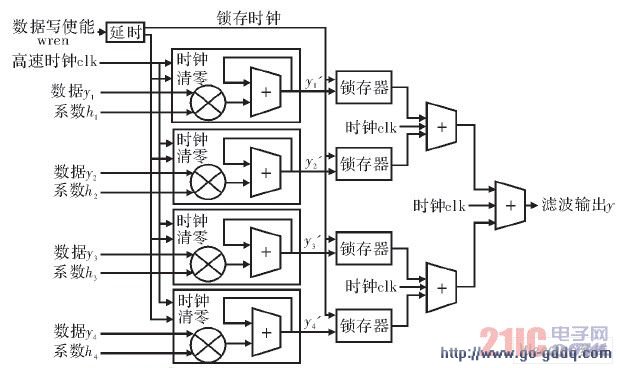

乘累加模块负责将输入的数据和系数进行乘累加运算,每256个时钟周期输出一个滤波结果。其实现框图如图8所示。

图8 乘累加模块实现框图

输入序列缓存模块输出的数据y1~y4和滤波器系数存储阵列输出的相应系数h1~h4在该模块进行乘累加运算。每256个时钟周期,计算完1个采样点数据的4个部分y1’~y4’,由锁存器锁存,经两级流水线加法器后得到最终滤波结果y,然后将累加器清零,开始准备下个采样点数据的计算。其中,锁存器的锁存时钟及乘累加器的清零信号都由输入序列的写使能wren经过相应的延时处理后得到。

3 仿真结果

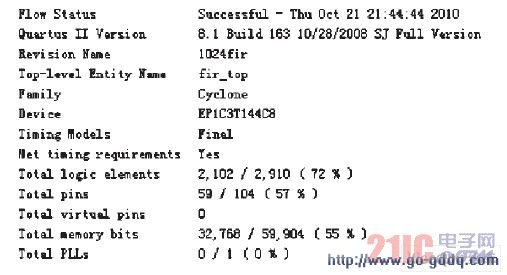

对设计的均衡滤波器进行综合编译,编译报告如图9所示。

图9 编译报告

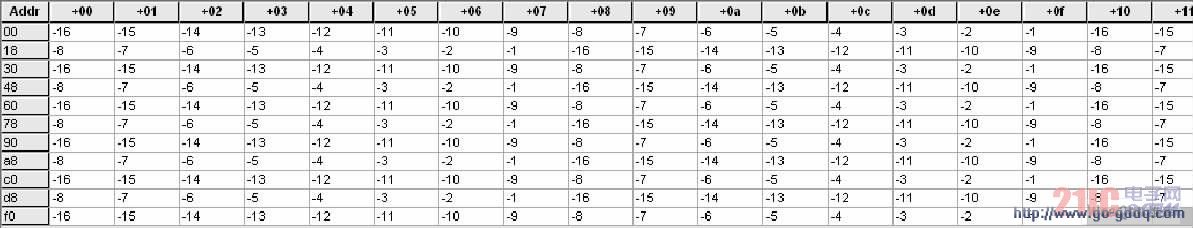

可见该1 024阶FIR均衡滤波器在EP1C3系列FPGA内得以实现,仅占用其约70%的逻辑资源和约50%的存储空间。为了验证该设计功能,将滤波器系数利用存储器初始化文件进行初始化,存储的系数如图10所示。

图10 滤波器初始化系数

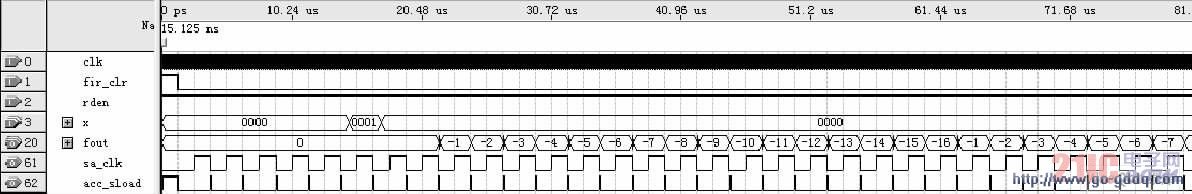

为了直观验证,输入序列x取为δ序列,即x中只有1个数据为1,其它为0。根据滤波器及卷积的相关知识,输出结果y=x*h=δ*h=h,即为滤波器系数。仿真结果如图11所示。

图11 滤波器仿真结果

输入序列x只有1个采样时钟周期为数据1,其它全为0,fout为输出的滤波结果。可见结果为-1~-16的重复数据,与图10所示的滤波器系数一致,滤波器工作正常。

4 结束语

利用EP1C3约70%的逻辑单元及约50%的存储空间,设计了1024阶FIR数字滤波器,并通过重载系数,可实现多种频率响应的均衡特性,实现了简易数字均衡滤波器的功能,达到了设计目标。