FPD-Link II有效负载

在每一个像素时钟周期内,28个"次符号"在差分I/O上经过时分多路复用,转换成一个串行数据流。嵌入的有效负载包含24个颜色位、3个定时信号(水平同步-HS、垂直同步-VS和数据使能-DE)以及附加位。互连线路速率为28x像素时钟。在65MHz下,该速率转化为1.82Gbps。串行数据流由前端的"CLK1"HIGH 位和末尾的"CLK0"LOW位限定,由此可在每一个帧之间实现高低电平的平稳过渡,令串行器的PLL可以参照其进行同步并提取嵌入的时钟信息。两个附加位("DCA"和"DCB"位)位于每一个帧中间,它们包括嵌入在DCA 和 DCB位过渡过程的定时信号。有效负载位为了降低谐波电磁干扰和改善信号质量,经过了随机化、平衡和加扰处理,同时为交流耦合建立了直流平衡。

由于电缆连接越长,发射器和接收器模块之间越有可能出现接地电位漂移,交流耦合接口方案则可通过在传输线中采用串联电容实现电势解耦。串行器中的直流平衡编码器和相应的解串器中的直流平衡解码器可在串行链路上实现高低位之间的均匀分布,以防止ISI(符号间干扰)效应和由电容引起的静态模式的阻塞。通过在两端配置电容,该方案也可以在电缆损坏或者对地或板上净电压出现短路时提供输入/输出短路保护。随机化和不规则性不仅能保证良好的眼图开度,同时还能最小化互联线路的电磁干扰,总体来说其编码效率高于85%。

增强的信号调理能力

信号调理技术在推动长距离高速连接方面发挥了至关重要的作用,在串行器端采用了信号还原特性,图4是一个信号还原操作的例子。这一串转换的比特流,依次为0、1、000和1,图形顶部给出了单端(SE)波形,可以在真值和输出端子处相对于地电位进行测量。图形底部给出了差分(DIFF)信号,相当于在其端子范围内接收器输入端的差分电压摆幅。对于第一次转换,发送的第一个信号是0,形成全差分摆幅。下一次转换是一个1,同样是全电压摆幅。接下来在C、D和E时间帧中是一系列0,其中第一个0是全电压摆幅。随着之后时隙D和E中第二个和第三个0的到来,幅值将会下降,表示被信号"还原"了。因此电缆中的静电荷将受到限制,否则它将会随着时间增强。这使得在时隙F发送的末位1又形成全差分摆幅。信号还原特性通常是在传输线路中平衡高低频信号的内能。总体效果就是清晰的信号眼图张开,在由1或0组成的长序列之后是以一个单独的比特位转换。信号还原层是可编程的,以便为特定电缆媒介调整至最佳补偿水平。

此外,信号还原特性在可调差分输出电压(Vod)方面有不错的效果,即它可以使长电缆传输的差分输出电压(Vod)加倍。信号还原不需要大幅降低接收器输入的信号幅度就能做到信号恢复。解串器的输入端集成了一个电缆均衡器,在再生全部信号波形时,此功能相对输入信号而言等同一个高通滤波器,可以部分消除由传输媒介引起的低通滤波器效应。均衡器在1.5dB到12dB的增益之间具有可编程性。当然,所有增强的信号处理特性也可以协调使用,为长电缆传输中的无差错数据恢复建立足够的眼图开度。

扩频时钟

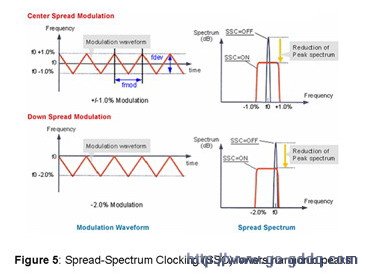

解串器通过一块集成可配置的扩频时钟(SSC)生成器得到增强。在接收器输出总线端,这会导致输出时钟频率和数据频谱随着时间推移而以几十KHz的低调制率产生轻微变化。如图5所示,频率变化可以发生在名义像素时钟中心频率附近("中心扩频调制"),或朝向更低的频率("向下扩频调制")。频谱扩展百分比可高达±2%。扩频时钟将峰值能量分散在更宽的频谱范围内,从而大大降低了电磁干扰噪声水平,而不是在同一时间点上、以恒定频率来转换所有输出,此时的辐射噪声集中在一个窄频段内,所有输出数据都与输出时钟同步,这使得数据和时钟得到有效扩展。特别是DS90UR906接收器输出具有低压(LV)CMOS接口选项,可以大大降低电磁辐射。

增强的诊断能力