通过输入数据移位实现DAC相位调整

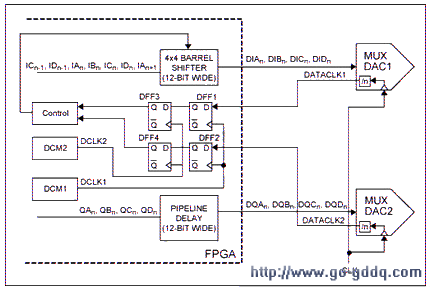

可以利用Xilinx FPGA中先进的数字时钟管理程序(DCM)来检测两个MUX-DAC的数据时钟之间的相位差异(图6)。DCM1生成一个与DATACLK1和DATACLK2相同频率的时钟。以时钟周期的1/256为间距对DCLK1的延迟进行动态调整。触发器DFF1和DFF2在每个时钟周期对DATACLK1和DATACLK2进行一次采样。如果DFF1在DATACLK1为低时采样

|

DATACLK1,DFF1会输出固定的“0”。如果DFF1在DATACLK1为高时采样DATACLK1,DFF1会输出固定的“1”。所以DFF3和DFF4可在任意时钟相位定时,与DCLK1的延迟设置无关。通过将DCLK1的延迟进行分级,使用DCM1的动态延迟调整功能以及读取DFF3和DFF4的输出,我们可以得到基于DATACLK1和DATACLK2上升沿的延迟设置。根据延迟设置,我们可以计算出为了保持MUX-DAC1和MUX-DAC2输入数据的同相,MUX-DAC1的输入数据需要延迟的DAC时钟周期数。FPGA中4 x 4桶形移位器的实现可使数据等待时间以一个DAC时钟周期为增量进行改变(参见图6)。

MAX19692有四个并行数据端口A、B、C和D。输入DAC的数据序列是

An、Bn、 Cn、Dn、An+1、Bn+1、Cn+1、Dn+1、An+2等。12位4 x 4柱形移位器(图6)允许输入MUX-DAC1的数据延迟-1、0、1或2个CLK周期。因此可以进行数据等待时间的调整直到两个DAC的输出数据同相。这样的话,两个DAC的数据时钟可能相距几个整数时钟(CLK)周期且不再改变。由于DAC的建立和保持时间以数据时钟为基准,所以两个DAC的数据时序必须不同。可以通过驱动DAC的FPGA中的多个DCM来实现。

图6. 利用FPGA中桶形移位器的实现完成MUX-DAC的 同步

每个DAC使用一个PLL实现DAC同步

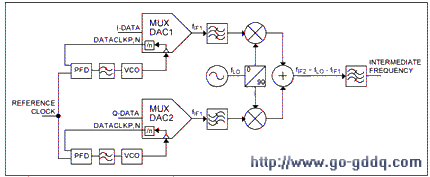

如果DAC使用锁相环(PLL)合成器来定时,那么同步两个DAC的方法就是每个DAC使用单独的PLL (图7)。DAC1和DAC2的LVDS数据时钟输出相位与参考时钟相比较。这样的话,DAC的内部时钟分频器在时钟生成PLL中作为反馈分频器使用。

图7. 每个DAC使用一个PLL实现MUX-DAC同步

这种方法中,两个DAC的建立和保持时间相匹配。但是这种方法有两个缺点,两个PLL会带来额外的成本且PLL的相位噪声极限可能会造成性能极限。

结论

MAX19692为2.3Gsps、12位、可工作于多个奈奎斯特频带内的DAC,具有集成的4:1输入数据多路复用器,是I/Q应用中的理想器件。当I/Q应用中MAX19692的使用被强调时,所讨论的方案同样适用于其它DAC和应用,比如在多于两个通道应用中使用的MAX5858A。本文所推荐的方案适用于任意数量的DAC。为了对 高速 器件进行正确的同步,还必须考虑与电路板引线相关的延迟。

上一页 [1] [2] [3] 下一页

关键词:

0

Copyright © 2007-2017

down.gzweix.Com. All Rights Reserved .

页面执行时间:120,953.10000 毫秒