2.1.3 Ӧ��ע������

�������ģ��������Ĺ����Դ�����ȶ��Ժã����ڵ�Դ�ĸ�Ƶ�������ײ������䣬�����ڿ������ģ�����������Դ���ŵĵط���Ӧ���ã������̣Ƶ�ȥ����ݡ�Ϊ�˷�ֹ���ٵ���������仯�����ص�����Ͻ�ģ���Դ�����ģ������������ֵ�Դ��ģ���ԴӦ�÷ֿ���ģ���ԴӦ���ڣ��֡������ķ�Χ�ڣ����ֵ�ԴӦΪ�������֣�ͬʱ�����ܵؿ�����Դ���ã����������������̣Ƶ��մɵ��������и�Ƶ�˲����������ã����̣Ƶ�������˳���Ƶ������

����Ϊ�˺ܺõؽ��գ��ģ�����������������źţ�Ӧ������С���Ը��ء����ģ������������������һ���̶������ת�����ʣ����֣����һ�����͵ģãͣϣ��ż��ϲ���Լ�У�����Ƶĵ��ݣ����ÿ������ת�����У���������������ơ����֣�����Ķ�̬��������������һ�������̵�ת����̬������

����2.2 �ƣɣƣ�����

�������ģ�����������������ʸߴ�����������ͣ���������˸ߵ������ʣ����ֱ���ãģӣеģţͣɣƽӿڽ��գ���ʹ�ģӣи��ɹ��ء����⣬����洢����ϵͳ���ܼ�ʱ�ؽ������ݣ��ϴε����ݻ����ϱ��´ε����ݸ��£�������ݶ�ʧ����˱�����ø��ٻ��档Ŀǰ���õĻ����Ϊ�ƣɣƣϡ��ӣң��ͼ�˫�ڣң��͵ȡ�˫�ڣң��ͺͣӣң��ʹ洢���ϴ��������Ը��ӵĵ�ַ�����������ڣƣɣƣ�оƬ������˳������������������Բ�ͬ������д��Ͷ�����������Χ��·�����Ա����ѡ�ãԣɹ�˾�Ĵ���ʽ�ƣɣƣ� �ӣΣ������ãԣ���������Ϊ���ݻ��档

�����ӣΣ������ãԣ���������һ�ָ��ٵģ����������������ģƣɣƣ���������ȡ�ٶ���߿ɴ���ͣȣ������ݷ���ʱ��ɴ����������ڣ̣ģã˵�������д�룬�ڣգΣã˵������ض������ƣɣƣϵ�״̬��ͨ��״̬λ���������ƣգ̣̣����գ����ţͣУԣ٣����������ȣƣ��Լ����գ����������ƣ����ţ���á��ӣΣ������ãԣ�������ֻ���ϵ縴λ��

����2.3 �ģӣ�����

�������ڣ��ģõĸ�������������ãģӣн���ʵʱ�������кܴ�ѹ�����ڣģӣн�������֮ǰ�������Ƚ��������±�Ƶ�Խ��������ʡ�ͨ���ԣģӣ��㷨������������������ԣɹ�˾�ģԣͣӣ������ã������������������Ҫ����Ϊ����ģӣУ��ԣͣӣ������ã���������Ƶ�ɴ�����ͣȣ��������ٶȿɴ�������ͣɣУӣ����������ⲿ�洢���ӿڣ��ţͣɣƣ�֧�ָ���ͬ�����첽�洢�����ԣƣɣƣ��кܺõ�֧�֡�

2.4 Ӳ���ӿ����

����Ϊ�˱�֤���ģ��������IJ�������ź�ȷ����Ч������ģӣУ��ڣ��ģ���ģӣ�֮�佫��Ƭ�ƣɣƣϲ��У�����˫�ƣɣƣϻ���ṹ�����ԣ����������߿������ӵ��ģӣеģţͣɣƽӿڣ�����������ͼ����ʾ��ͨ�����ֽӿ���ƣ��ڳ�����ãţͣɣƵģ������������߿��ȵ�ͬʱ���������ʵ���˲������ݵ���ż���룬Ϊ�ģӣе������˲��ͣƣƣ������ṩ�˷��㡣

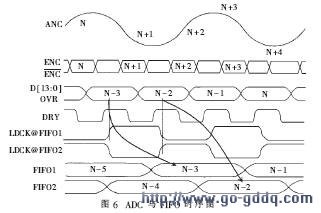

�������Ƚ��ܣ��ģ���ƣɣƣϵĽӿڡ����ģ��������ģ���λ�����ź�����Ĥ������������������ƣɣƣϵ���������Ĥ������������������ƣɣƣϵģģ����ͣģ������գ����ģң��źž�����Ƶ��һ·���ӵͣ���λ�ƣɣƣϣ��ģ̣ģã����ţ���һ·�����ǡ��ŷ�������ӣƣɣƣϣ��ģ̣ģã����ţ� �ģңٽ�������ǣţΣãϣģ��źŵ�ͬƵ�����ӳ��źš���ʱ��ͼͼ���п��Կ������ڣģңٵ������ش��������źţĤ�������������������ģң��źſ�ȷ����Ϊ�����ƣɣƣϵĴ����洢ʱ���źš�������Ƶ��ģģң��ź��������ش����津���ƣɣƣϣ��ͣƣɣƣϣ���дʱ�ӣ�����ż�����źŷֱ���벻ͬ�ģƣɣƣϡ�

�������Ž��ܣƣɣƣ���ţͣɣƵĽӿڡ����ڶ��ƣɣƣϵIJ����������õ��ţͣɣ��첽�洢�������źţ����ʹ�ܣ��ϣźͶ�ʹ�ܣ��ңš��ãţ����ⲿ�ռ�ѡ���źš���ͼ������ϵ�ɿ����������ϣ���ãţ��Чʱ���ϣ���Ч��Ƭѡʹ�������ƣɣƣϡ����ãţ�ͣ��ң�ͬʱ��Чʱ���գΣã���Ч���������������ڴ�ʱ���г�ʼ���������ңŻ�����Ϊ����ƽ��������ʹ�գΣã˲��������أ��ƣɣƣ������ݱ�������ͼ�������ƣɣƣϵİ����źţȣƾ���һ�����롱���������ģӣ��ⲿ�ж����ţţأԣߣɣΣԣ��������в��ϼ��ȣƹܽ�״̬���������ƣɣƣϽԴﵽ����ʱ�����롱������ɵͱ�ߣ������ش����ģӣ��ⲿ�жϣţأԣߣɣΣԡ��ģӣ������ģͣ���ֱ�Ӵ洢����ȡ����ͻ���ķ�ʽ��ȡ�ƣɣƣ����ݡ��ƣɣƣϣ���������Ϊ�ͣ���λ���ƣɣƣϣ���������Ϊ�ߣ���λ���ϲ�Ϊ����λ���ݶ���ģӣ��ڲ��洢�ռ䡣