�� ���� ��ҵ����������һ����������Զ������������������༼���ͷ���ѧ���Ա��㷺���ܡ����磬Ӳ����������Verilog�ı���ʹ��RTL�ۺ���80������ھͿ�ʼӦ�á�

��������֤����ʹ�û����������֤����ѧ���㷺���ܵı����ƶ��������˱�������OSCI��TLM(����ģ)2.0��ACCellera�ı�Эͬ���潨ģ �ӿ� (SCE-MI)�ȱ������˶��������Ȥ���ǡ����⣬��֤����Ŀǰʹ��Ӳ�����ٺͷ��������ٻ����������֤��

����ΪʲôҪʹ������

����Cadence Design SystEMSϵͳ��ƺ���֤��Ʒ���������ܼ�Ran Avinun��ʾ����ϵͳ��ƽ�ģʱ��ͨ��Ҫʵ������Ŀ�ꡣ����һ�������������������ڶ���������ϵͳ���壬�������ǿ�ִ�й淶��������������мܹ�Ȩ����������Ҫ���ǣ���Avinun˵��

���������ʺ�������Щ�ط���Ϊʲô��ƹ���ʦϣ��������ģ�Ϳ�ʼ�������ս���Щģ����Ӳ������ʵ�֣��������û���˵������������ʵ�ֿ�ö��ģ�⡣������㽫ģ��д��TLM����ͨ�������������֤����ͨ�ţ��Ϳ�ʵ�ָ����ٵ�ģ�⡣��Avinunָ����

��������TLM����һ���ô��ǵ����������졢�����ס���һ����˵��������дTLM�������ɵĴ�����٣��ҵ���������ʱ��Ҳ���١������ṩ��һ�����ֹ��ܺ�ʵ�ֵĻ��ᣬ��Avinun�ơ�

����������Ҫ��дһ���ܱ������ܵ�ģ�ͣ�Ȼ��Լ���ֿ������ǿ�����ʱ��Լ����������ض����սڵ㣬��ʱ��仯�Ķ����������һ��Ӧ��ת����һ��Ӧ�û��һ���ڵ�ת����һ���ڵ�ʱ������ģ�ͻ�����ס���Avinun˵��

�������������ʹ�õ�

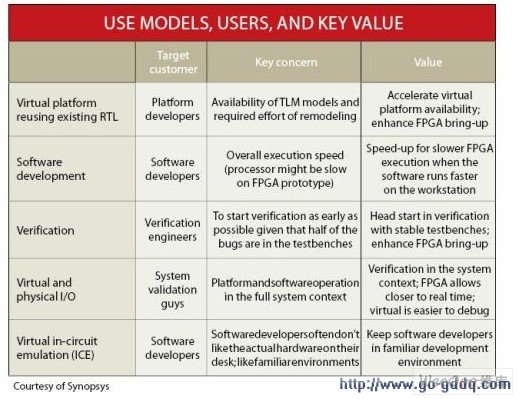

������Synopsys��ϵͳ�� ������� ��ƷӪ���ܼ�Frank Schirrmeister���ܣ���̸��TLMʱ������������ʹ��ģ���ѳ�����(���±�)�������б���λ���Ǹ��õ������

��������������£������Ƶĺܴ�һ�����Ѿ���RTL��д����ʱ����ѷ�����һ�ֻ��ģʽ��ģ�ⷽ��ѧ�����У����е�RTL�� FPGA �����С����ͬʱ���������������ģ���TLM��Ϊ�����������С�

���������ڶ�λ������֤ʹ��ģʽ������������£�������һ������ƽ̨��Ȼ����RTL����֮ǰ����һ���������������ǽ�����ʱ��TLMʵ�ֵġ�

���������Ǵ���ʱ��ģ�����ֶ�������Ҫ���ǵ���֤��������Schirrmeister˵���������� �ֻ� ����Ϸ�����ض���ʱ�������ܽӵ绰�𣿽�������ƽ̨����������ں����ض�����Щ�������Ϊ�����������ڴ������ϵ�������ɡ�������������Ŀ��ʹ�����ǡ���

����������ʹ��ģʽ��*��ϵͳ���ⲿ����֮�����ϵ����Щ��ϵ�ȿ�����������Ҳ����������I/O��̬��

���������磬���� USB�ӿ� ����ϣ���ڸ߱�������������ʵ���罨�����ӡ��������һ�ӿڻ������ڣ������������ķ�ʽ���佨�����ӣ��������������������������Schirrmeister˵��

������ȻUSB��һ������˵���������ӣ���Schirrmeister ���о�������ŶӲ��ø÷���ѧ���ֻ��н������߽ӿڵ����ӡ�����ͨ�� FPGA �����������ʵ�ֵġ�

�������ĸ�ʹ��ģ�������Զ�����������������Ϊ��������Ӳ���в�������һ����µ����ɽ�����������ԭ����ʽ���ֵ�������������������������������£���Ҫ����һ�����������������ڸû����µ�����������Ա��������Ҫ֪����������������FPGAԭ�ͻ�������ƽ̨�ϡ�������Schirrmeister ���ԣ�����һ�֡�ʹ����������Ա����ʵ����֮�⡱��������

���������(Ҳ�����һ��)ʹ��ģʽ��һ���漰��FPGA�Ϲ���Ӳ��ԭ�͵ĸ���������������������ʵ֤����FPGA�������д���������ѡ����ΪFPGA������ǹ�ע DSP ����Schirrmeister ˵��ͨ����������ģ�ͱ���תΪ����ʵ�֣������ͨ������Ӳ��ԭ���Լ�����������д�����ø�����Ĵ����ٶȡ����⣬������Ҫ����������ijЩ���֣��ɻ�÷dz���������ٶȡ�

���� ���� �������ݱ�

����Ϊʵ�ֽ�һ����չ��TLM����������Ҫ���������Զ�����������Ƕ��ʽ���������������֤������֤����ʦ��Ҫ��ֱ�ӵIJ��ԡ���Schirrmeister˵����һ�����Ϸ�չ�仯��Ҫ��������������ɣ�������У��.�Լ�������TLM����������ϵͳ�� оƬ (SoC)�ۺ���֤�ĸ��Ƿ�Χ���������ģʽ�����ɡ����Ǽ���Լ���������ʹ�õ��������ʱ������TLM���������������

����TLM�д��ںϵĵ�����Ҫ������ʵ�ֵ�ֱ�����ӡ������dz���һ����Ϊ��TLM��GDSII������Schirrmeister ˵�� ����ȥ���������硣һ����������ƽ̨������һ�����ظ��ۺϡ�������Ϊ�ڽ���ij��ʱ�����������罫�϶�Ϊһ����

������������ƹ���ʦ�Լ� EDA ��Ӧ����˵�����������������ƽ̨���ۺ�(HLS)����֮�佨�����ӡ�

������һֱ��������ͼ��TLM������Щ���硣��Forte Design Systems���г������۸��ܲ�Brett Cline˵����������ʼ���Ǹñ�ֻ��������֤��û�����ۺϡ���TLM�淶��ȱ����һЩ�dz���������Ӳ����ƶ���������Ҫ�Ķ��������磬û��ר�еĸ�λ���ơ���

����OSCI�ڲ���Ŭ�����յ�����TLM 1.0������������������TLM 2.0�汾�� �����Ƕ�OSCI TLM 1.0��������չ������һЩ�����������������һЩ�£�Ҳ�����ۺϵ��˽⡣��Cline˵����TLM 2.0��һ�����ӹ�ע�ۺϵı�������Ҫרע�ڻ��� ���� ��ϵͳ����TLM 2.0�������������������ϵͳ������Ӧ�ñ�̽ӿ�(API)��

����Cline��Ϊ��������֤����ʦ��ʵ��֮��ĺ蹵������ƽ̨��HLS�Ƿֿ��ġ������Ǵ������Ƕ������������������һλ��֤��(������ƽ̨�Ƕ�����)��������һλ��SystEMC����Ӳ����Ƶ�ʵ���ߡ���Cline˵�������ڣ���֤���Ѿ���ʶ����TLM������һ��������д�������ʵ�ֵĿ���;����ͬʱ��ʵ����Ҳ����ʼ������ν�һЩ�������ɽ����е÷dz����ϵͳģ�͡���

����Schirrmeister��ʾ����ȥ���ֳ��̺��û��ڸ���ʱ�Ѿ�ʹ��������ƽ̨��/��HLS��������TLM 2.0��Ϊ������������������������ģ�⣬������HLS���Dz��ࡣʵ���ϣ��������������ۺ��Ӽ����ƶ�TLM 2.0�����HLS��������ҵ����Ӧ�Եķ�չ������˵��

����Ӳ������

��������������֤��һ����Ҫ����ǽ���TLM��ʵ�ּ�������֤��Ӳ���������Synopsys�Ƴ��������ԭ��ϵͳHAPS-60ϵ����ΪConfirmaƽ̨����ɲ��֡���������˼Virtex-6 FPGA������HAPS-60ϵͳ�Ƕԡ��Խ����ǹ����ߵ����»�Ӧ����ȥ�漰����ԭ�ͼ���ʱ�����ٸ����⡣

������ϵ�в�Ʒ���������ͺţ�HAPS-61(�� FPGA�����450��������)��HAPS-62(˫FPGA��900��������)�Լ�HAPS-64(4 FPGA�� 1800 ��������)��������������һ��HAPS-50ϵ�е�һ�����⣬HAPS-60�������ܵ�ʱ��Ƶ�ʸߴ� 200MHz ��

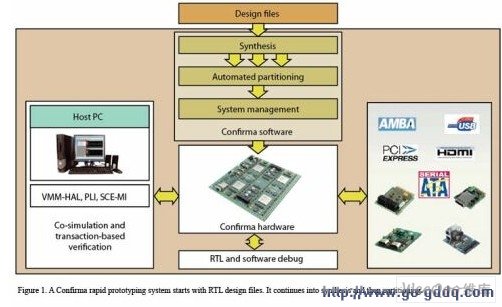

������Confirma����ԭ��ϵͳ(ͼ1)�������һ�ָ������Ǵӹᴩ�ۺ�ʼ�յ�RTL����ļ���ʼ�������ڿ���ԭ�Ͱ��϶���ƽ��зָϵͳ��Confirma����ִ����һ�ָ���̣����Ҹ�����������Ŀ����һ��HAPS�塣Ȼ���û��Ϳ��Խ���ģ��ԭ������Ľӿ�ʵ�������Լ�Эͬ����ͻ����������֤����Ľ�������ӵ����������С�

ͼ1��һ��Confirma����ԭ��ϵͳ��RTL����ļ���ʼ�����Ž����ۺ�Ȼ�����ƽ��зָ

�������ڵĿ���ԭ��ϵͳ��������������ͻ����һ��������FPGA��������������ƹ�ģ���ٶ�Ҫ������𡣹�ȥ���Ը�����Ľ���취�ǻ������ã��������ΪȨ��֮�ƣ������ջ�����ϵͳ���������ܡ�

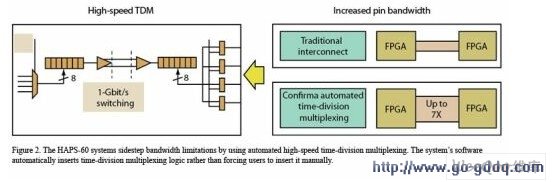

����HAPS-60ϵͳ�����Զ�����ʱ�ָ��ñ�������Щ�������ơ���ϵͳ�������Զ�(������ǿ���û��ֶ�)����ʱ�ָ�����(ͼ2��)�������չ�ȥ�ķ�ʽ����Ҫ������RTL����ļ�����Synopsys����Ӫ��ҵ����չ����Doug Amos˵��

ͼ2��HAPS-60ϵͳͨ�������Զ�����ʱ�ָ��ñ����˴������ơ���ϵͳ�������Զ�(������ǿ���û��ֶ�)����ʱ�ָ�����(ͼ2��)

���������Զ�����������ʵ����һ�����Զ�ʱ��ͬ����ϵ�1Gb�������ʡ����൱�ڽ��ܽŴ���Ч�����7�����Լ���ƽ��ϵͳ�������30��(ͼ2��)��

��������UMRbus�ܹ�ʹ��HAPS-60ϵͳ���������ڻ����������֤(ͼ3)��UMRbus��һ�ָ����ܡ�����ʱͨ�����ߣ�����Ϊ���а���FPGA�� �洢�� ���Ĵ�����������Դ�ṩ���ӡ�

������UMRbus���������� ��· ����ƣ���Amos˵����֧���������úͼ�صĶ�����ϵͳ��Զ�̷��ʡ�������ƻ����ͼ�ع���(ͼ3��)���������ڡ����û����Կ�����ơ�������ơ�������ơ��ض��洢�������Ծ�������Amos˵��

����UMRbus��֧�������Ƚ�ģʽ�����������������֤��Эͬ����(ͼ3��)�� ���û��ɱ�д������ʵ�ָ�����ƻ����ͼ�ع��ܣ��� Amos˵����ϵͳ����������������ĵ���ģʽ����Щģʽ��ȥ�����������ġ�

�������漰�����������֤ʱ��ͨ��ʹ��SCE-MI 2.0����ӿ�(ͼ4)��HAPS-60ϵͳ���Դ��������֤ʱ�䡣�������ǿ���SCE-MI 2.0��Ŀ�ģ���Amos˵����SCE-MI�ӿ�ʹ�����������������������������ݵ�Ӳ�����Լ�Ӳ�����������ü��������� ������ ���͵Ļ�������ģ����ʵ�������������

�������ڣ�HAPS-60ϵͳʹ���ַ������ͷ���ѧ������һ������ԭ��ϵͳ��ʵ�֡�SCE-MI������ԭ�Ͳ���ʹ�ø���������ϵͳģ����ԭ�ͺͷ�����֮��Ľ��ޣ���SCE-MI��ʹ�����ʵ�ֵ����֣���Amos˵�������ǣ�����HAPSӲ�������мIJ���ƽ̨ʱ���ٶȿɱȷ����10,000����

����֧��TLM 2.0

�����ṩ֧�ֻ����������֤����һ��Ӳ����Ӧ��EVE���������ZeBu����ƽ̨��Ʒ���������˶�TLM 2.0����֧�֡� TLM 2.0�� Open SystEMC Initiative(OSCI)����SystemCģ�ͻ������Ժ����õĽӿڱ��������ǵ������ڴ˱����������˷���������˶�������˵��������ǻ��������Эͬ���棬��EVE-USA�ܾ���Lauro Rizzatti˵��

����EVE��ͨ��һ�������� ������ (ͼ5)ʵ���˶� TLM 2.0��֧�֡���������֧�ֶ��Ŀ��ͷ����ˡ���Ϻͷ���ϴ���ӿڣ��Լ���ɢ��ʱ(LT)����ɢ��ʱʱ�����(LTD)�ͽ��ƶ�ʱ(AT)���뷽ʽ��

������ϵͳ�����û����Խ�����ƽ̨��TLM 2.0�������������Լ��Ƚ�SystemVerilogӲ����֤���������������ڷ���������ZeBu TLM-2.0��������������һ�ֿ�ʵ��������ZeBu���������Ļ������Ŀ��żܹ���������ZeBu���������Ȼ�������EVE����������Ŀ¼��������ZEMI�C3���ɡ�ZEMI�C3��EVE���������������߹���ģ��(BFM)����ΪSystemVerilog���������ñ�����ʹ�ñ�д���ھ�ȷ��BFM�Լ���C++��SystemVerilog����ƽ̨������Ϣ������÷dz����ס�

������Rizzatti�ƣ��ڻ��������ģʽ�У�70����80����EVE�ͻ�ʹ��ZeBu�����ڼĻ���C��ѭ��ģʽ(����������ģʽ)�У�����Ҳ���ܽ������ڵ��á�����ʹ��������������Ȼ��Ϊ����ģʽ�ĺô������ø�ģʽ������˵��

����EVEӪ���ܼ�Ron Choi��ʾ����TLM 2.0��֧��ʹEVE�ķ������ڻ������Է������һ��¥���������������Ƕ�����һ�����ӿڡ���������ͨ��һ��ר��API��ʵ�֡�����һ�ַdz����õķ���ѧ�������ڶ��ڻ��ڱ��ķ����и�ǿ�ҵ�������˵��

����TLM 2.0�������������������ƹ���ʦΪ�ŽӲ�ͬ��Ʒ�����д��ͬ����������⡣��һ����˵��ESL��������������ͨ��������Խӿ�(PLI)���ӵ�RTL ģ���� ���Լ�ͨ��API����C/C++�������ӵ�����������Rizzatti˵������Ҫ��������Բ�ͬ�Ľӿڱ�д��ΧӦ�á������ڱ��ʱ����д�������еĻ������ԡ�һ�����õİ취��ʹ�ö����˻�������� TLM 2.0����ʹ�û����迼�ǵײ�ʵ�֡������������Ƿ�ʹ��SystemCģ�;Ͳ���Ҫ�ˡ���