摘要:为实现CAN总线与计算机的通信,便于CAN总线系统调试,提出一种基于 FPGA 的CAN总线转换USB接口设计方案。利用USB总线与计算机通信,详细论述了FPGA对 SJA1000 与 CY7C68013A 的具体控制过程以及CAN总线的通信实现。这种方法数据传输速率高,设计灵活,可扩展成多路总线的通信接口。目前已成功应用于空间相机下位机系统的地面检测设备中。

CAN总线是现场总线的一种,因为其成本低、容错能力强、支持分布式控制、通信速率高等优点在汽车、工业控制、航天等领域得到广泛应用。但是计算机没有CAN总线接口,为了进行CAN总线的调试,必须具有专用的适配卡才能实现与计算机的通信。目前常用的CAN 转换器 是基于 单片机 设计的,一般只适用于单路CAN总线的数据转换,可扩展性差。

在小卫星相机下位机系统中使用了多种总线,如CAN总线与卫星管理计算机的通信;RS422(或 RS485 )总线与成像单元等下行单元的通信。在进行相机下位机系统地面调试时,可能需要多种总线转换器。采用FPGA将不同总线协议转换成USB2.0、 RS232 等可与计算机直接交换数据的协议,可增强设计的灵活性,降低设计的成本和复杂性,且可实现多路总线的数据通信接口。

这里以CAN总线通信接口为例,详细论述了基于FPGA的CAN总线转换USB接口的设计方案。

1 系统硬件组成

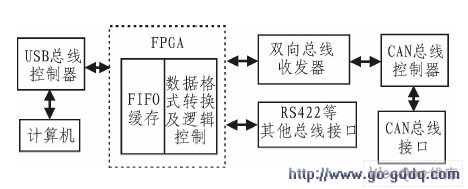

实现CAN总线与计算机双向通信接口的核心是FPGA。它首先接收来自CAN总线的数据,保存在FPGA内部设计的FIF0缓存中,经过内部数据格式的转换后,由USB控制器读取并上传给计算机。而总线数据注入过程的数据流向与之相反。FPCA选用 Xilinx 公司的Spartan3的 XC3S200 ,系统硬件结构如图1所示。

图1 硬件结构框图

1.1 USB接口 电路

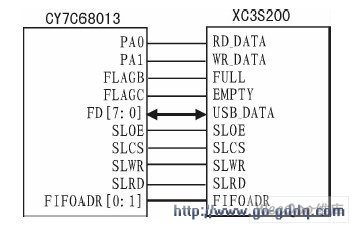

USB是一种支持即插即用及热插拔的串行总线,它具有传输速率高、连接灵活、使用方便等优点。 CYPRESS 公司的 EZ-USB 芯片CY7C68013A支持USB2.0协议,通信可靠,传输速率可达480 Mb/s。CY7C68013A工作在SLAVE FIF0异步通信方式下,接口电路如图2所示。

图2 CY7C68013A接口电路

SLAVE FIFO异步写周期中,高电平需维持70ns,低电平需维持50ns,理论最高传输速率为8Mb/s,而CAN总线的最高传输速率为1Mb/s,符合通信要求。端口PA0~PA1用作USB控制器端向FPGA发送读写命令的控制线,由USB固件程序配合上位机端自定义请求代码产生PA端口的控制信号。另外使用了 EEPROM 芯片 24LC128 存放USB固件程序。

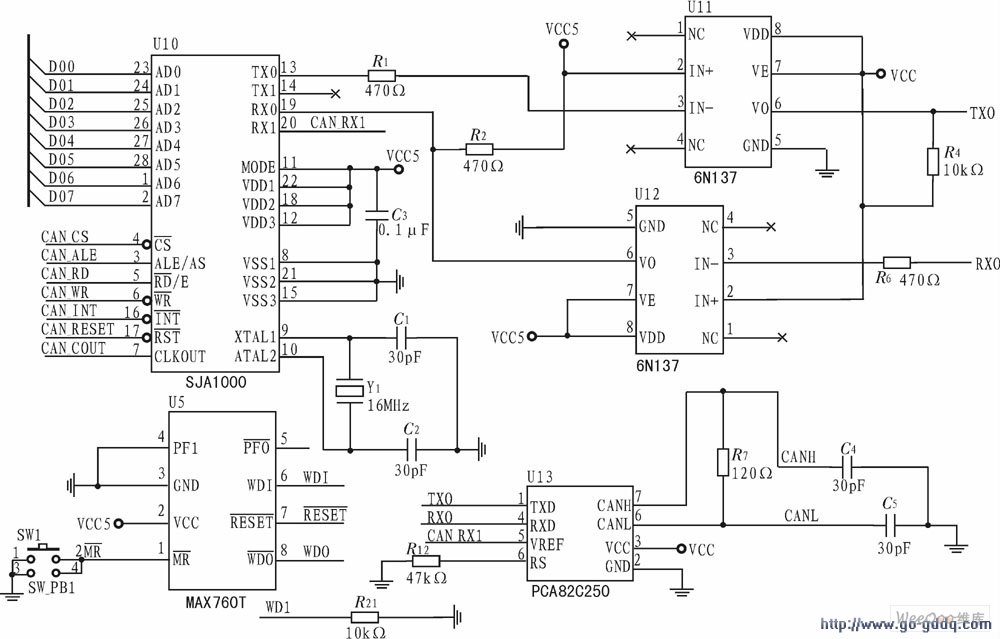

1.2 CAN总线接口电路

选用 Philips 公司的SJA1000作为CAN控制器,采用 PCA82C250 作为CAN收发器,并在CAN控制器与收发器之间使用 6N137 进行光电隔离,以增强抗干扰能力。将MODE引脚接高电平即SJA1000工作在 INTEL 模式, 引脚与复位芯片 MAX706T 的RESET引脚相连,进行全局复位。在FPGA与SJA1000连接时需要使用741V164245电平转换器完成CAN总线5 V TTL电平向3.3 V FPGA I/O电平的转换。另外,SJA1000的RX1引脚与PCA-82C 250的VREF引脚相连,使用输入比较器旁路功能,可减少内部延时,增加正常通信的总线长度。具体的接口电路如图3所示。

引脚与复位芯片 MAX706T 的RESET引脚相连,进行全局复位。在FPGA与SJA1000连接时需要使用741V164245电平转换器完成CAN总线5 V TTL电平向3.3 V FPGA I/O电平的转换。另外,SJA1000的RX1引脚与PCA-82C 250的VREF引脚相连,使用输入比较器旁路功能,可减少内部延时,增加正常通信的总线长度。具体的接口电路如图3所示。

图3 SJA1000接口电路

2 FPGA逻辑控制程序

2.1 SJA1000逻辑控制

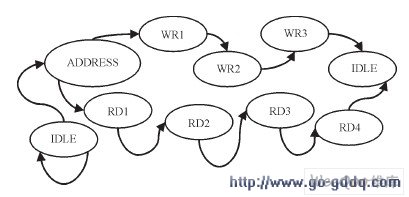

由于SJA1000地址线与数据总线复用,FPGA不仅仅要产生SJA1000读写控制引脚的信号逻辑,还需要模拟单片机等处理器产生对SJA1000的寻址信号,实际上是一个向SJA1000写地址的过程。根据SJA1000技术手册的时序要求,要完成对SJA1000内寄存器的正确读写,接口逻辑必须在地址锁存信号ALE为高电平时将SJA1000的寄存器地址当作数据写入,然后在ALE和片选信号 为低电平后使能SJA1000的读写控制信号(WR或RD)。SJA1000的逻辑控制采用状态机的方式完成,状态机流程图如图4所示。起始态为IDLE态,当接收到数据读写等命令时,进入ADDR-ESS态,向SJA1000写入相应寄存器的地址值。然后根据命令类型决定下一个态是写寄存器状态(WR1~WR3)还是读寄存器状态(RD1~RD4)。以写寄存器为例,在WR1态ALE、

为低电平后使能SJA1000的读写控制信号(WR或RD)。SJA1000的逻辑控制采用状态机的方式完成,状态机流程图如图4所示。起始态为IDLE态,当接收到数据读写等命令时,进入ADDR-ESS态,向SJA1000写入相应寄存器的地址值。然后根据命令类型决定下一个态是写寄存器状态(WR1~WR3)还是读寄存器状态(RD1~RD4)。以写寄存器为例,在WR1态ALE、 等信号置为非有效态。将

等信号置为非有效态。将 置为有效状态;在WR2态ALE、

置为有效状态;在WR2态ALE、 为非有效态.而将

为非有效态.而将 信号置为有效态,在时钟的下降沿将数据写入寄存器。WR3状态保持

信号置为有效态,在时钟的下降沿将数据写入寄存器。WR3状态保持 有效,WR信号变为无效,进入IDLE态,一次写周期完成。

有效,WR信号变为无效,进入IDLE态,一次写周期完成。

图4 SJA1000逻辑控制状态机流程图

2.2 SJA1000读写数据流程控制

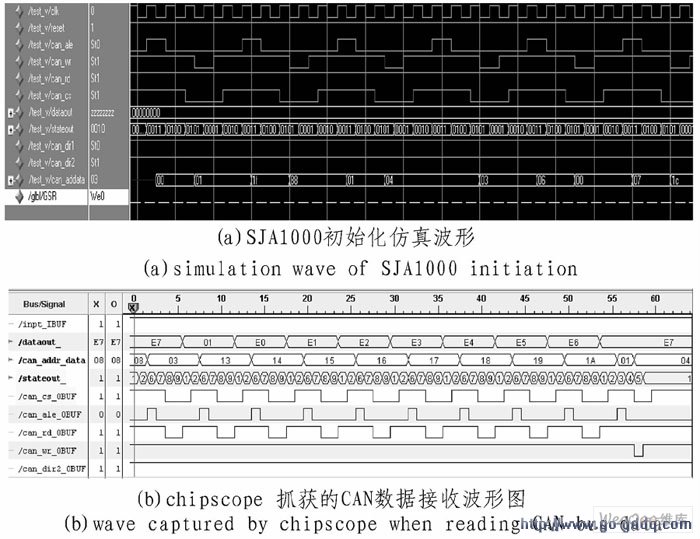

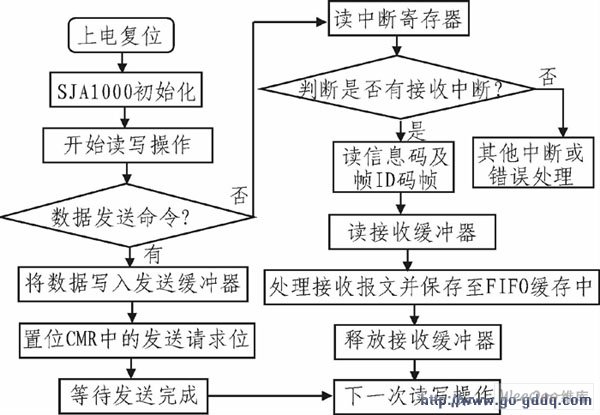

FPGA对SJA1000控制程序包括SJA1000初始化、SJA1000读数据、SJA1000写数据等部分。SJA1000的初始化是在复位模式下进行的,在复位模式下分别设置时钟分频器CDR、总线定时器(BTR0、BTR1)、输出控制寄存器(OCR)等重要寄存器。SJA1000通信波特率由总线定时器决定,需要与后端节点的波特率相同才能进行节点间的正常通信。FPGA上电后需要延时一段时间.等待SJA1000复位完成才能进行SJA1000初始化。初始化仿真波形如图5(a)所示。SJA1000内部有一个接收缓冲器和一个发送缓冲器。FPGA对SJA1000的读写操作,实际上对这两个缓冲器的读写控制。当FPGA接收CAN总线数据时首先读取SJA1000中断寄存器IR判断是否有接收中断。如果有接收中断到来则开始读取缓冲器内的8字节数据,然后释放接收缓冲器(写命令寄存器CMR)。使用Xilinx公司的Chipseope软件进行板上测试,测试数据为(E0,E1,……E7),抓取到的波形如图5(b)所示。FPGA读写SJA1000的流程控制图如图6所示。

图5 SJA1000逻辑控制波形图

图6 SJA1000读写控制程序流程图

2.3 CY7C68013A通信控制程序

CY7C68013A提供一种量子FIFO的处理架构,使USB接口和应用环境直接共享内部含有的4 K FIF0空间。本文CY7C68013A的控制是以异步SLAVE FIFO方式实现的,FPGA对CY7C68013A的逻辑控制实际上是对CY7C68013A内部FIFO的异步读写控制。设置CY7C68013A端点2为批量输入端点(FIF0地址为00),端点6为批量输出端点(FIF0地址为1O)。FPGA判断CY7C68013A的PA[1:0]端口电平,当PA[1:0]为01时,FPGA将接收到的CAN总线数据写入端点2对应的FIF0空间并上传给上位机,PA[1:0]为10时,FPGA读取端点6对应的FIFO内数据。FPGA对CY7C68013A的时序控制严格按照芯片手册完成。

由于USB数据包与CAN数据帧是基于两种不同协议的数据格式,因此在FPGA内开辟了2个512x8bit的FIFO缓存,并要进行必要的格式转换。例如,当从USB总线端注入的数据大于8字节时,需要将数据分成多帧传送给CAN总线;当数据小于8字节时则在数据后填充0。另外,在数据传送给CAN总线之前还需要添加适当的帧信息与帧识别码。

3 软件设计

3.1 USB固件程序

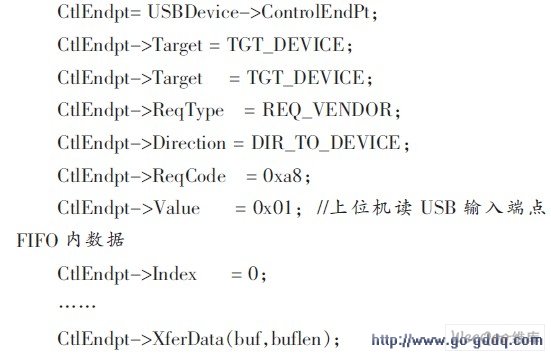

USB固件程序是在Keil工具上开发完成的,除了进行必要的端点及寄存器配置外,程序中使用了自定义请求命令。自定义请求码通过USB控制传输的方式传送给固件,固件程序需要响应自定义请求码的请求信息。本文使用的自定义请求码为Oxa8,在响应代码中设置端口PA[1:0]电平值,产生USB控制命令,代码如下所示。SETUPDAT对应控制传输端点的Value值,由上位机应用程序设定。

3.2 USB驱动程序及应用程序

使用 Cypress 公司提供的CY7C68013A通用驱动程序CyUSB.sys。上位机应用程序使用VC编写,也是基于Cypress提供的C++类库文件CyAP-I.lib设计完成的。使用的主要函数包括:BeginDataXfer、FinishDataXfer、XferData等函数。应用程序中设计了独立的数据接收线程,线程函数中不断地发送USB数据读命令,并完成批量输人端点的读操作。当有数据读入时,与主线程之间采用事件的线程同步方式,将数据读入计算机内存并保存。以下是线程函数中用于发送USB控制命令的控制传输代码:

4 实验调试与结果

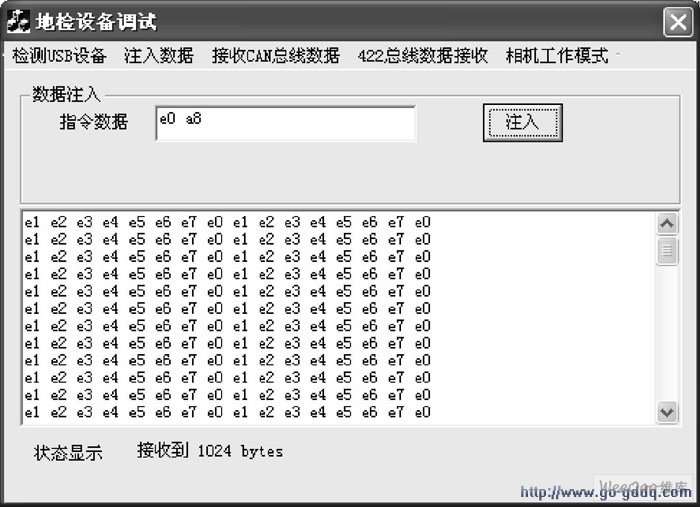

为验证设计的正确性,使用了周立功公司的USBCAN-I产品,与目标电路板组成双节点通信,2个节点设置相同波特率500 Kb/s(BTRO= 00,BTR1=1Ch)和相同帧格式,由测试软件ZLGCANTest发送一组数据(e0h,e1h,……,e7h),上位机应用程序接收到的数据如图7所示。反过来由上位机应用程序注入指令数据e0h,a8h,周立功软件接收到的数据为e0h,a8h,00h,00h……。经实验表明,数据收发正确,近距离通信时,通信速率可高达1 Mb/s。

图7 上位机应用程序图

5 结论

使用该方法设计的CAN总线转换器优点在于:使用USB总线完成CAN总线与计算机的数据交换,不会影响CAN总线的整体通信速率;通过FPGA控制完成通信接口的设计,可扩展性好,灵活性强,稳定性高。作为空间相机下位机地检设备的一部分,FPGA同时还可以完成RS422等总线的通信控制。