在不断发展的许多重要市场中都可见到多CPU设计。网络路由是率先广泛应用多CPU设计的领域之一。大多数新一代网络处理器都是基于多CPU设计的。除了标准NPU,目标ASSP也在利用多处理器建立更加优化、更有应用针对性的路由解决方案。许多情况下,特殊ASSP是比标准NPU更为有效率的解决方案。ASSP可以集成恰当的物理接口或考虑片上存储器的大小,亦或提供最佳的处理器配置。

相关的应用如DSLAM和基站或高性能网络存储设备也在利用分治法建立高性能的可编程解决方案。出于成本和/或功耗的原因,甚至终端用户设备也在开始利用多CPU实现最高的性能密度。机顶盒、住宅网关,甚至智能移动设备也都在采用多CPU——不仅再是一个RISC处理器和一个DSP,而是多个RISC处理器和DSP。

如何构成理想CPU内核

用于多CPU设计的理想处理器内核必须具有以下一些重要特性。

首先最重要的是,它必须可提供出色的性能密度。多CPU设计的目的是在每平方毫米或每瓦特拥有尽量多的性能集合。能够以最小空间或最低功耗实现最高MIPS的解决方案才是最佳选择。

另一个需求是处理器间有效的通信。即使许多多CPU设计是软件关联的,仍然需要大量的处理器间的通信。如果没有用来支持处理器之间通信的结构,那么SoC设计师就必须进行开发。这些工作不仅要耗费大量时间,同时也给设计带来了另一方面的复杂性。对于处理器间通信的支持可简化SoC设计师的工作量,也可以缩短开发时间,还可以将分区边界的低效率降到最低。

多CPU设计的另一个挑战的是调试。内核之间是相互影响和彼此依靠的,因此在调试SoC时了解这些交互行为十分重要。CPU需要具备内置能力,在进行调试时能够完全互动。如果没有这种能力,SoC调试可能会迅速变成一场灾难,也许更糟——变得完全不可调试。优秀的多CPU调试工具对于CUP的支持也十分关键,这样才可以保证SoC设计师发挥嵌入CPU的调试能力。

另外需要考虑的是配置和执行CPU内核的灵活性水平。在多CPU设计中,重要的是在最大限度地降低面积和功耗的同时使性能最大化,而一个高度可配置、可合成的CPU有助于设计师考虑特定应用的面积、功率和频率。利用硬内核或不能配置的内核是不可能做的这一点的,它将严重限制执行的选择。

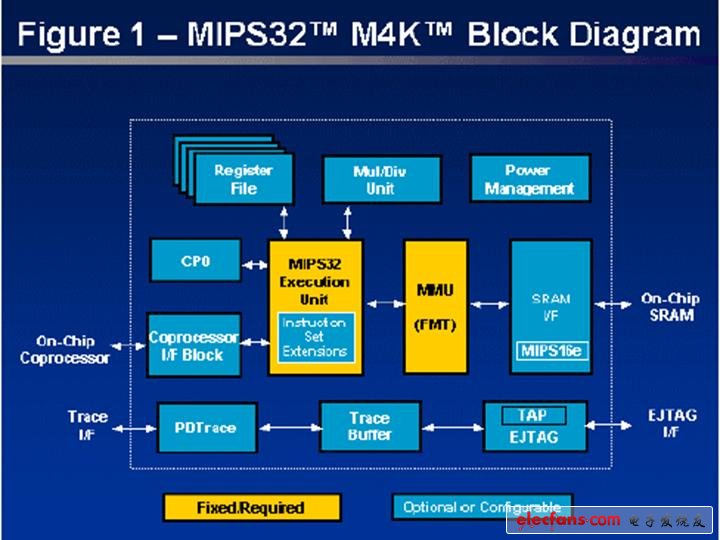

考虑到上述因素,MIPS科技发布了专门针对多CPU设计的CPU内核。MIPS32 M4K内核具有高性能,不过或许令人惊奇的是,它也是小型的低功耗内核,而且还是可合成的,具备低延迟存储器系统。

让我们来看看M4K内核的映射是否满足上述要求。

性能密度

性能密度的定义是,以最小的面积提供最高的性能,或是在最小面积上实现最低的功耗。M4K内核可用紧凑的面积和功率限制来提供高性能。该产品可提供大约1.35Dhrystone(整数和逻辑运算性能测试)MIPS/MHz(无需使用其他内核使用的受到置疑的编译器窍门),采用普通0.13μm工艺的产品可在240MHz(最差情况下)条件下运行,采用更高性能的0.13μm工艺的产品可在300MHz条件下运行。

作为性能密度公式的分母部分,M4K内核是一个非常小和功耗极低的处理器。该产品可配置成像32K门电路,也就是小于0.3mm2的尺寸,而且仍然可以保持整个MIPS32架构的兼容性。该产品的功耗极低,采用0.13μm工艺时可低至0.10mW/MHz。

该内核还具有新的增强型MIPS架构,可改善重要应用功能的性能。这些功能包括优先化、矢量中断及多达4个寄存器上下文,以减少中断延迟和开销。位域和字节级指令可提供高效率的信息包处理。

该产品包括自定义指令集扩展,SoC设计师可利用该功能执行所需的专用的、高度集中的应用优化,并利用定制指令扩展M4K中业界标准的MIPS32指令集。任何寄存器到寄存器或立即存取寄存器指令都可以进行添加。定制指令可为单周期或多周期,也可支持新用户状态。这些自定义指令是由内核RTL、合成脚本和仿真模式支持的,并可使用GreenHills、Cygnus和Mentor等公司的业界标准开发工具。

此外,可能最为重要的是,M4K内核具有上述所有特性,同时可保持MIPS32的完全兼容性,并可使用MIPS CPU广泛的软件和工具。事实上,该内核是惟一具有定制指令扩展和业界标准架构的有效的可配置处理器。

处理器间的通信

在多CPU设计中,处理器间必须进行通信以控制共享资源的使用。在今天的大多数多CPU设计中,存储器关联完全由软件控制,所以通信所需的普通高速缓存关联是不能使用的。

M4K内核通过外部化MIPS架构中的加载关联(LL)行为和条件存储(SC)来支持多CPU信标,以保证对系统逻辑进行必要的监控。此外,SYNC指令的行为可提供存储器排序壁垒,以保证正确的排序语义,也可以提供信号接口,为系统设计提供最大的控制和灵活性。

如图2所示,当执行典型的信标存取码序列时,LL和SC指令可提供原子型读-改-写序列,而无需锁定整个系统。

例如,在测试和设置安全自旋锁定时,LL指令可在信号接口产生一个读指令,它作为LL由系统进行确认。然后系统按照该地址设置监控。如果另一个处理器写入这个受到监控的地址,监控的通过/失败标记就会被清除。当CPU执行SC指令时,系统逻辑根据监控状态有条件执行对存储器的存储。通过/失败指令会返回处理器,而软件通常会重复失败序列,直到成功为止。

同样,SYNC指令的语义外化可保证系统存储器壁垒的正确行为。

如图3的例子所示,SYNC被放置在一个共享缓冲器的最后的存储与可释放一个控制语义的存储之间。当执行SYNC指令时,CPU向系统逻辑发送信号,通知CPU等待同步响应。一旦系统确认指令可以执行,就将信号发回CPU,允许其后的任务或存储继续执行。一个简单的系统可能会等待所有未完成处理事务的完成,而一个更为复杂的系统可在其列队中保持顺序,而缓冲器可以更快地做出响应。这两种系统中,CPU软件和硬件机制是相同的。

M4K处理器间的通信功能是一种优异的解决方案,得到了业界标准开发工具的全面支持。计划利用M4K内核实现多CPU的设计师,可以利用这些功能快速而容易地实现内核之间的通信,缩短设计时间并降低实现风险。