【摘 要】 通过设计实例详细介绍了用VHDL(VHSIC Hardware DescriptionLanguage)语言开发FPGA/CPLD的方法,以及与电路图输入和其它HDL语言相比,使用VHDL语言的优越性。

关键词:VHDL,FPGA/CPLD,EDA

1 引 言

EDA(电子设计自动化)关键技术之一是采用硬件描述语言(HDL)描述电路系统,包括电路结构、行为方式、逻辑功能以及接口。就FPGA和CPLD(分别是现场可编程门阵列和复杂可编程逻辑器件的简称)开发来说,比较流行的HDL主要有VHDL、ABEL-HDL、AHDL等,其中,VHDL对系统的行为描述能力最强,已被IEEE确定为标准HDL,并得到目前所有流行EDA软件的支持,进而成为系统设计领域最佳的硬件描述语言。用VHDL设计电路系统,可以把任何复杂的电路系统视为一个模块,对应一个设计实体。在VHDL层次化设计中,它所设计的模块既可以是顶层实体,又可以是较低层实体,但对不同层次模块应选择不同的描述方法(如行为描述或结构描述)。本文在设计实例中详细介绍了用VHDL语言开发FPGA/CPLD的方法,以及与电路图输入和其它HDL语言相比,使用VHDL语言的优越性。

2 设计实例

一个复杂电路系统的设计都是采用自顶向下将系统按功能逐层分割的层次化设计方法。在顶层设计中,要对内部各功能块的连接关系和对外的接口关系进行描述,而功能块实际的逻辑功能和具体的实现形式则由下一层模块来描述。在系统的底层设

计中,如采用VHDL进行描述,由于其对系统很强的行为描述能力,可以不必使系统层层细化,从而避开具体的器件结构,从逻辑行为上直接对模块进行描述和设计,之后,EDA软件中的VHDL综合器将自动将程序综合成为具体FPGA/CPLD等目标芯片的网表文件,无疑可使设计大为简化。下面以数字钟的设计为例予以说明。

数字钟的功能主要有:

·能够对秒、分、小时进行计时(按每日24小时计时制)。

·秒、分、小时位能够调整。

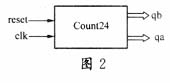

根据数字钟的功能要求,可将数字钟分为四个功能块:秒脉冲发生器、计数器、校时器和显示电路。而这些功能块又可进一步分割为更小的模块,如计数器模块可再分为秒、分、小时计数器。其它功能块的细化过程不再详述,数字钟的系统框图如图1所示。图中,P1键为自动计时、校时、校分和校秒四种工作状态选择键,P2键为系统处于校时状态时对时、分、秒进行校准的校时键,32.768kHz为作为脉冲源的晶振频率,经14级2分频器分频在其最高位、次高位以及第五位输出端分别可获得1Hz、2Hz和1024Hz的脉冲信号,这三个脉冲信号分别用作计时脉冲、校时脉冲和显示电路的扫描时钟。下面用VHDL语言设计底层的小时计数器。小时计数器为一个24进制BCD码计数器,其模块示意图如图2所示。reset、clk分别为异步清零端和时钟端,qb和qa分别为十位和个位的四位BCD码输出端。该模块计数方式的实现比较复杂,当十位数为0或1时,个位进行10进制计数,当十位数为2时,个位进行4进制计数。如用电路图描述,则必须选择和调用若干门、触发器或宏单元,并需对所调用的器件进行合适的控制。而若采用VHDL语言对其功能进行描述,问题则显得非常简单。

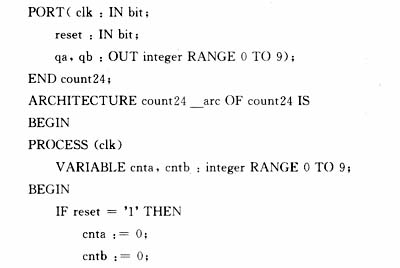

下面是用VHDL语言设计的24进制BCD码计数器count24模块∶

ENTITY count24 IS