2 电路设计

2.1 采样网络的时间常数匹配

如前所述,直接利用MDAC以取消SHA模块会带来潜在的孔径误差的问题。由图2可知,MDAC与Sub ADC通过两组不同的开关与电容组成的采样网络对输入信号采样。由于采样网络直接面对快速变化的输入信号而非采样保持电路输出的直流信号,因此,采样网络时间常数的失配会造成MDAC与Sub ADC采样到的电压不同。并且这种误差会随着输入信号频率的增加而增加。当误差超过数字校正电路所能处理的范围时ADC的性能就会下降。为了克服时间常数失配引起的ADC高频性能的退化,两个采样网络的时间常数不能失配过多。另外,第1级电路的位数越低,数字校正电路可以处理的误差电压就越大,这可以放宽对时间常数匹配的要求。

当输入频率是fIN,幅度是Vref的正弦波时,如果MDAC与Sub ADC的采样网络的时间常数分别是τ,τ+△τ(△τ表示他们之间的失配),且当采样网络的带宽远高于输入信号的带宽:

对于1.5位的结构,数字电路可以校正的误差范围是1/4Vref。为了不让孔径误差超过这个范围,必须使得:

![]()

因此只要两者之间的时间常数的失配不超过40%,孔径误差就会落在数字电路的校正范围以内。实际上,数字校正电路处理的误差还应该包括比较器的失调电压,所以应该保证MDAC与Sub ADC的采样网络时间常数失配小于40%。

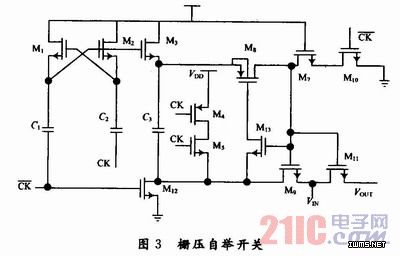

本文使用的Bootstrapped开关作为输入开关。这种开关在导通时可以保持导通电阻恒定,这样,因为开关导通电阻与输入信号相关而造成的非线性会被大大降低。具体电路如图3所示。M1,M2,C1,C2组成电荷泵,使M3的栅极与低电平为VDD,高电平为2VDD的方波信号相连。在CK为低电平时,M3和M12同时导通,使电容C2充电至电源电压。此时M10,M7导通,M11的栅极通过M7和M10与地相连,M11处于断开状态。当CK为高电平时,M10,M3,M12断开,M8,M9导通,这样,C3上的电压加到M11的栅源两端。可见在CK为高电平时M11的栅源电压一直固定在VDD,与输入信号无关。对于Sub ADC与MDAC,输入开关的导通电阻可以分别表示为:

由于Bootsrapped开关在导通时,开关管的栅源电压保持在VDD,因此开关的导通电阻只与开关管的尺寸有关。这样开关导通电阻因与输入信号相关而产生的非线性就被大大降低。

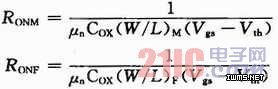

为了保持两条信号通路的时间常数(τ=RC)一致,有:

![]()

于是,MDAC与Sub ADC的采样开关的尺寸应该满足:

![]()

式中:RONM,RONF,CS,CC分别指MDAC与Sub ADC的采样开关的导通电阻和采样电容;(W/L)M,(W/L)M分别指MDAC与Sub ADC的开关管的尺寸。

2.2 运算放大器

运算放大器是流水线ADC中最重要的单元模块,其消耗了整个ADC的大部分功耗。为了避免运放有限增益与带宽对ADC的转换精度产生影响,运放的开环增益和单位增益带宽必须满足:

![]()

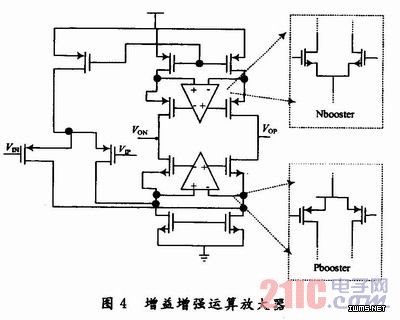

设计的运放如图4所示。主运放采用折叠式结构以扩大输出摆幅。自举放大器商样是两个折叠式放大器,其输入管分别采用PMOS管与NMOS管输入。这样主运放中靠近电源与地的晶体管只需一个过驱动电压大小的压降,这可以避免辅助运放限制主运放的输出摆幅。辅助运算放大器可以显著提升运算放大器的整体增益,但是它会与主运放形成局部反馈环路。该环路会在传输函数中引入零极点对。零极点对会延长运算放大器的建立时间。