・上一文章:数字集成芯片构成的频率计数器设计

・下一文章:一种全集成型CMOS LDO线性稳压器设计

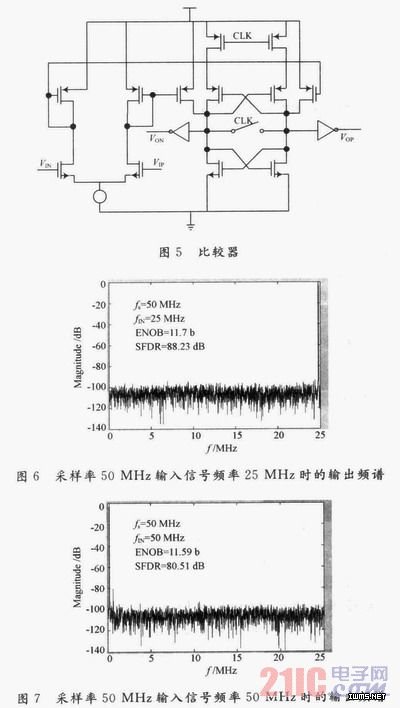

2.3 比较器

使用数字校正技术可以放宽对比较器失调电压的要求,简化比较器的设计。设计的比较器由3级组成:预防大级,重建锁存器和输出级,如图5所示。使用预防大级,可以减小传输延时。由于预放大器的增益不需要很大,使用40μA的尾电流,这样可以减小整个比较器的静态功耗。在CLK为高时,输出端箍位于阈值附近,在CLK变为低后,重建锁存器形成正反馈环路,将预放大级输出的电压差不断放大,直至将输出分别拉到电源和地。输出级采用反相器,提升比较器的驱动能力与避免亚稳态效应。

3 结果与分析

为了验证ADC的性能,在ADC的输入端加入单一频率的正弦波,并对输出波形进行傅里叶分析。图6是采样频率是50 MHz,输入25 MHz正弦波时的输出频谱图。此时电路的SNDR=72.19 dB,SFDR=88.23 dB,对应ENOB=11.70 b。图7是输入50MHz正弦波时,输出信号的频谱图,此时电路的SNDR=71.59,SFDR=80.51 dB对应ENOB=11.59 b。可见,通过取消SHA和匹配ADC的两条通道的时间常数,在输入低频和高频信号时ADC始终具有较好的线性度。在采样频率时50 MHz时,ADC的功耗为128 mW(不含参考电压产生电路)。表2列出了ADC的主要性能参数。

4 结语

设计了一个12位50 MS/s的流水线ADC,该电路使用0.18μm 1P6M工艺实现。通过取消前端采样保持电路,消除了采样保持电路引起的失真和带来的功耗开销;经过仔细匹配输入时间常数,保证ADC在输入高频信号时依然保持足够线性度;使用运放缩减技术,进一步辟低了功耗。仿真结果表明,该ADC满足设计要求。