・上一文章:松下MD2L机芯彩电资料

・下一文章:小型功率UPS电源九个注意事项

随着半导体工艺的飞速发展和芯片工作频率的提高,芯片的功耗迅速增加,而功耗增加又将导致芯片发热量的增大和可靠性的下降。因此,功耗已经成为深亚微米集成电路设计中的一个重要考虑因素。为了使产品更具竞争力,工业界对芯片设计的要求已从单纯追求高性能、小面积转为对性能、面积、功耗的综合要求。而微处理器作为数字系统的核心部件,其低功耗设计对降低整个系统的功耗具有重要的意义。

本文首先介绍了微处理器的功耗来源,重点介绍了常用的低功耗设计技术,并对今后低功耗微处理器设计的研究方向进行了展望。

1 微处理器的功耗来源

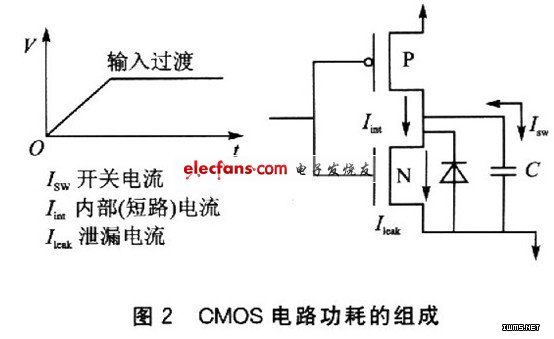

研究微处理器的低功耗设计技术,首先必须了解它的功耗来源。高层次仿真得出的结论如图1所示。

从图1中可以看出,时钟单元(CLOCk)功耗最高,因为时钟单元有时钟发生器、时钟驱动、时钟树和钟控单元的时钟负载;数据通路(Datapath)是仅次于时钟单元的部分,其功耗主要来自运算单元、总线和寄存器堆。除了上述两部分,还有存储单元(Memory),控制部分和输入/输出 (Control,I/O)。存储单元的功耗与容量相关。

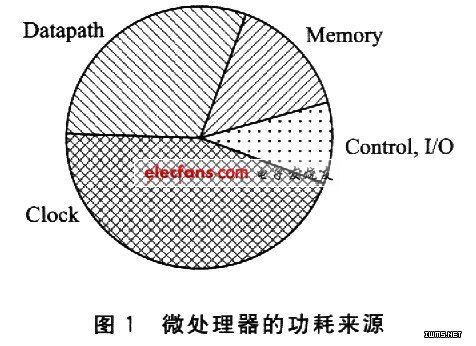

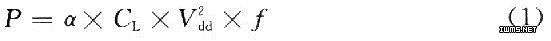

如图2所示,CMOS电路功耗主要由3部分组成:电路电容充放电引起的动态功耗,结反偏时漏电流引起的功耗和短路电流引起的功耗。其中,动态功耗是最主要的,占了总功耗的90%以上,表达式如下:

式中:f为时钟频率,C1为节点电容,α为节点的翻转概率,Vdd为工作电压。