・上一文章:基于单片机的集成编码PT2262解码器设计

・下一文章:51系列单片机IO引脚的驱动能力与上拉电阻分析

软件设计

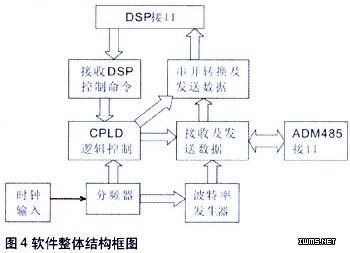

软件是指CPLD的VHDL程序,其主要由分频器、接收DSP控制命令、CPLD逻辑控制、波特率发生器、接收及发送数据和串并转换及发送数据六个软件子模块组成(图4)。

分频器模块主要是把20M赫兹的输入时钟频率分频为10M赫兹和2.5M赫兹的时钟频率,其中10M赫兹时钟主要是供给CPLD逻辑控制模块工作,2.5M赫兹时钟主要是供给波特率发生器模块工作。

接收DSP控制命令模块实际上是实时的采集DSP发来的控制信号并及时的将控制信号进行译码,译码完成后立即转送给CPLD逻辑控制模块。

CPLD逻辑控制模块是整个CPLD软件的核心,其接收到译码数据后,立即作出逻辑控制运算,并快速的控制接收及发送数据模块和控制串行转换及发送数据模块。

波特率发生器模块主要是为接收及发送数据模块提供2.5Mb/s波特率。

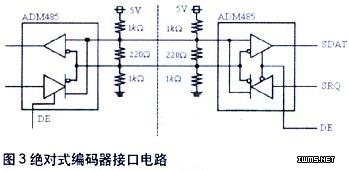

接收及发送数据模块是整个CPLD软件的重要组成部分,其主要负责与绝对式编码器高速通信,由于其通信方式是异步串行通信方式,因此其波特率、通信的数据格式及RS-485通信协议都要与绝对式编码器相同。

串并转换及发送数据模块主要是将接收到的编码器串行数据转换成并行数据,并将数据锁存在CPLD锁存器内,当CPLD逻辑控制模块控制其发送数据时,就将锁存在CPLD锁存器内的数据以并行的方式放送给DSP,供DSP进行运算控制用。

结语

本设计已经完成了硬件及软件的全部设计,读取带有绝对式编码器的电动机转子的任何一个位置数据只需31μs,通信速率可达2.5Mb/s,将本设计集成在伺服驱动单元中,驱动和控制电动机转数可达6000转/分,控制电动机转子的位置精度可达μM级。