2.1.4.1 中断控制器

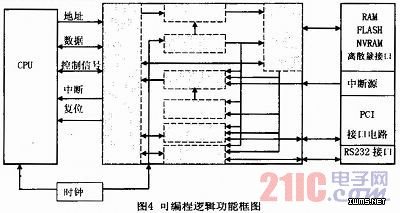

可编程逻辑采用IP核实现一个具有1路非屏蔽中断和16路可屏蔽中断的中断控制器功能。中断的触发方式(电平触发/沿触发)和16路可屏蔽中断的优先级软件可调。系统控制器在实现时使用了1路非屏蔽中断和11路可屏蔽中断,剩余资源可根据用户需求使用。

2.1.4.2 定时/计数器

可编程逻辑采用IP核实现一个3路独立的8位定时/计数器功能,其工作模式与MD8254的MODE2方式相同,每路定时器的输出使能和计数频率软件可调。系统控制器在实现时使用了两路定时器供操作系统使用,剩余的1路留可根据用户需求使用。

2.1.4.3 串行协议控制

可编程逻辑采用IP核实现2路RS232串行协议控制,用户可以通过软件对串行接口的工作方式(查询/中断)、串行数据的格式(数据位/起始位/停止位/奇偶校验等)和串行通信速率(9600-119200bps可调,默认38400bps)等参数进行设置。

2.2 软件设计

CPU模块使用VxWorks5.5操作系统,软件开发环境为Tornado 2.2。VxWorks操作系统具有实时性、可靠性、可剪裁性、支持众多的目标机、系统的开放性、丰富的环境工具和第三方支持等特点。VxWorks操作系统功能结构如图5所示。

CPU膜块的软件包括以下内容:a.FLASH编程工具;b.BIT测试程序;c.Vxworks操作系统:d.驱动程序;e.应用程序。

3 结束语

小型化的CPU模块,已成功应用在升级后的系统中,取得了良好的成效。除了总线传输速度提高(PCI总线最大传输速度可达132Mb/s)、使系统性能得到提升外,还具有以下特点:

(1)安装方式灵活,节约系统资源。CPU模块采用PMC板卡形式,占用空间小(面积下降33%),可以方便地安装在其它模块上,同时与典型的80486模块相比,重量下降70%、功耗下降15%,节约了系统资源。

(2)配置灵活,升级潜力大。CPU模块在本设计中作为PCI总线控制器(Host)使用,但是只要更改PCI9056的配置,并且对可编程逻辑做相应更改,即可作为PCI总线的主设备(Master)和从设备(Slave)使用。由于采用了SoPC技术进行可编程逻辑设计,CPU模块上还有可利用的空间进行功能扩展(例如增加I2C电路和网络接口),同时只要提高处理器和PCI接口的工作频率,即可进一步提高CPU模块的性能。

(3)通用性强,应用前景广泛。由于采用了标准的PCI接口和PMC外形,CPU模块可以方便地配置在一个PCI总线系统中,并且具有可灵活配置的工作方式(Host/Master/Slave)。同时为现有采用80486处理器计算机系统的升级,提供了可借鉴的模型,具有广泛的应用前景。