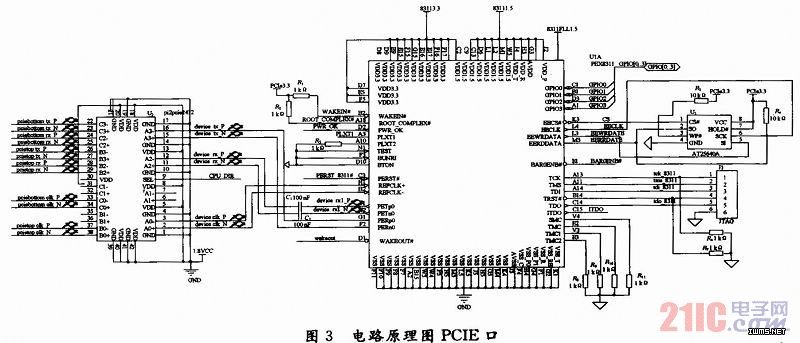

图3中接受、发送和差分时钟这3对差分信号线通过转接芯片变成了6对差分信号线。由主机板卡发出选择信号(cpu_dir),分别控制设备板卡是在主机板卡的上面还是下面。同时采用MAX6306芯片来链接PEX8311的复位端和PCIE接插件的复位端,同时实现了手动复位和LOCAL端的复位。

1.1.3 PEX8311的外围电路配置与LOCAL端接口的控制

PEX8311有几个类别的模式选择,分别是根联合体模式(Rootcomplex)与终端模式(Endpoint),根据需要这里选择了终端模式。此外PEX 8311还区分C模式,J模式,M模式。这三种模式解释如下:C模式的地址线与数据线是分开的,J模式下地址线与数据线是复用的,而M模式是针对了Motor的本地端CPU设置的。三种模式通过模式选择管脚选择,这里选择C模式作为工作模式。PEX8311有1.5 V,2.5 V,3.3 V三种电源供电以及一个模拟电源1.5VPLL。在配置寄存器方面,PEX8311有两个配置寄存器,分别是采用Spi-Compatible接口的PCIE配置寄存器和采用了Micro-Wire-Compatibel接口的本地配置寄存器。采用了Spartan-3an 1400 k来提供控制接口与高速缓存,选择这款FPGA主要因为它是有内部FLASH,不用再加外部的E2PROM。

由于PC/104是一种嵌入式的板卡,体积比较小,所以用这款FPGA是可以节省板上的空间。FPGA内部程序的编写是关键之一。这里采用Verilog,实现对PEX8311的控制,当上位机响应了中断后,对PEX8311发出读数信号。PEX8311通过LHOLD申请控制本地总线,待收到FPGA发出的LHOLDA响应信号后获得本地总线的控制权,并立即启动4 B突发模式。FPGA在收到有效的LW/R读信号和ADS地址选通信号后,发出Ready本地准备好应答信号。PEX8311开始从双口中读取数据,传输最后一个数据时,PEX8311发出BLAST信号,双口RAM使得读使能和输出使能无效。

1.2 系统软件部分的实现

该系统的软件部分是在Linux下实现的,在Linux中所有的设备都被看成文件来对待。在Linux内核中,设备驱动作为文件系统的一个模块存在。它向下负责与硬件系统的交互,向上通过一个通用的接口挂接到文件系统上面。从而和系统的内核链接起来。设备驱动为应用程序屏蔽了很多细节。使得应用程序对外设的操作就和操作普通的文件是一个样子的。利用PLX公司提供的开发工具,驱动的开发是比较方便的,本文系统中主要用到的是要编写一个中断服务程序:系统在收到中断,保存现场。进入中断服务程序。首选读取标志位,再马上清中断,之后读取响应RAM中的数据。最后恢复现场,完成操作。

2 系统PCB设计和高速信号的完整性分析

由于PCIE的传输速率较高,单向速率达到2.5 Gb/s。所以对板子的布线有严格的要求。叠层这里选用了8层PUCB板,有4个电源层,使得每个信号都能够屏蔽在电源层与地层中间。从而减少了信号的电磁辐射。对于PCIE的差分线部分:微带线要求差分线宽5 mil,间距小于12 mil,差分线间距离大于20 mil,同时与地层间距为3.5~5.5 mil。带状线要求线宽4 mil,间距小于11 mil,间距大于20 mil。且对于收发差分线,差分线长差距不能大于5 mil。这些都是为了能达到PCIE规范的要求,即单端阻抗55 Ω,差分阻抗100 Ω(偏差10%)而设置的。