・上一文章:基于MC9S12XS128的单片机开发板的设计

・下一文章:基于最小能耗的无线传感器网络路由算法

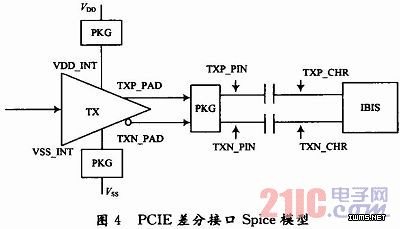

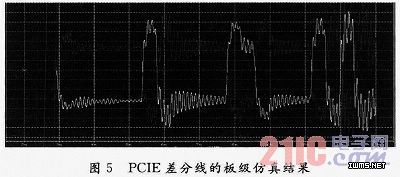

将上诉模型导入HSpice中,同时引入PCIESwitch芯片给出的IBIS模型与板子上面的差分线trace的rglc模型。输出端的仿真效果图如下,可以看出差分信号的幅值是可以满足PCIE规范的电气要求的。

3 结语

PC/104作为一种嵌入式总线标准已经被很多控制系统所采用,而PCIE/104接口的提出将未来最为流行的串行差分总线结构,引入到了这种嵌入式总线标准,从而为各种高速、高带宽的嵌入式系统提供了选择。目前该系统由于采用了PCIE总线,相比采用PLX9054实现的PCI接口具有明显的优势。