2.3 DMA模块介绍及初始化代码

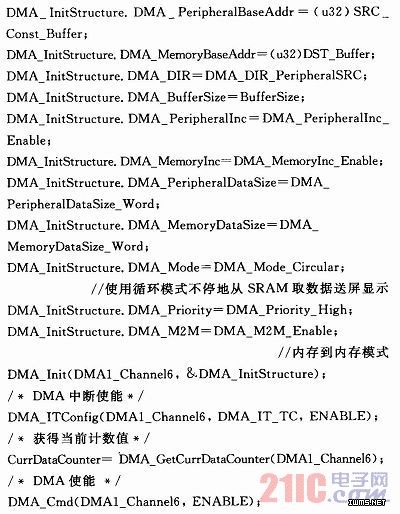

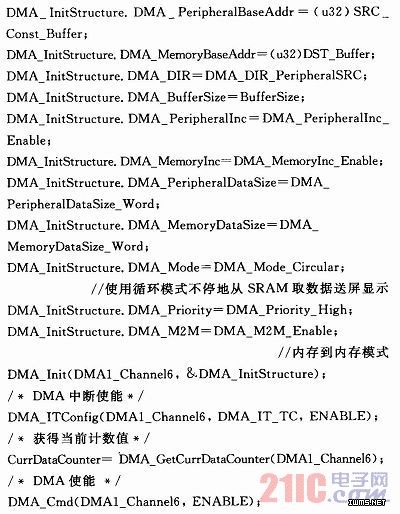

本文采用存储器到存储器之间的数据传输模式,由外部显存SRAM传输数据到FSMC接口来完成数据更新。DMA部分初始化代码如下所示:

2.4 屏接口时序的实现

由于RGB接口数字屏对时序要求相对来说比较苛刻,所以采用STM32103VCT6的高级定时器来产生精确的时间单位,并以此为最小的时间单位来产生相应的接口时序,STM32由定时器来控制对TFT的扫描,以保证足够的刷新率。扫描时,STM32的CPU仅仅参与对DMA的设置和显存的操作,由DMA控制器来直接从显存中读取显示数据并送至连接RGB数字总线上,不停地读写。这都是由DMA控制器来完成的,占用CPU的时间是有限的,从而有足够的时间来实现用户程序代码。

结语

经实际证明,本方案是可行的,能保证320×240点阵的TFT的刷新率,且留有足够CPU时间给用户程序。但是对于分辨率较高的彩屏,由于STM32主频的限制,刷屏速度会很慢,达不到应用要求,但是对于一些分辨率适当的彩屏还是能胜任的。

上一页 [1] [2] [3] [4]