・上一文章:第四代移动通信系统关键技术研究

・下一文章:应用多个单片机的液位监控仪

摘要:文中从控制信号和数据通路两个方面入手,设计了信号在不同时钟域之间的同步电路。采用直接锁存法和锁存反馈法来控制信号的跨时钟域传递,电路简洁、高效;采用异步FIFO (First In First Out)实现数据信号的同步,并通过格雷码和两级锁存来进行指针的跨时钟域传递,FIFO缓冲区的空满判断采用修改后的格雷码,对n+1位的编码可以节省(n2-n-2)/2次异或操作。该设计解决了信号跨时钟域传递时可能出现的亚稳态问题。

关键词:同步电路;异步FIFO;格雷码;亚稳态

随着系统应用需求的不断增多和集成电路技术的快速发展,大规模数字电路中常包含多个时钟域,设计中不可避免地要完成数字信号在不同时钟域间的传递,这时,如何保持系统的稳定,顺利完成控制信号和数据通路的传输就变得至关重要,这也是电路设计中最为棘手的问题之一。如果不采取一定的措施,控制信号和数据通路的接收方极易产生亚稳态信号,从而造成电路的同步出错。本文讨论了控制信号和数据通路的同步,提出了解决方案。

1 控制信号的同步技术

控制信号的同步分从快时钟域到慢时钟域、从慢时钟域到快时钟域的转换和异步输入控制信号的同步三种情况。分别采用直接锁存法和锁存反馈法来实现。

1.1 直接锁存法

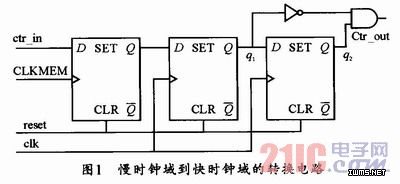

控制信号从慢时钟域到快时钟域转换时,由于控制信号的有效宽度为慢时钟域周期,需要做特殊处理,保证跨时钟域后有效宽度为一个快时钟周期,否则信号转换到快时钟域后可能被误解释为连续的多个控制信号。同步电路如图1所示,在快时钟域对控制信号进行两级锁存,由于第二和第三个触发器的输出延迟一个快时钟周期,将它们做一个逻辑运算,就可以得到有效一个快时钟周期的控制信号。