・上一文章:多波形雷达回波中频模拟器设计

・下一文章:一种710 MHz LTE天线的去耦合分析

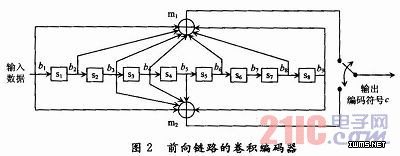

1.2 CDMA 2000系统中的前向链路卷积编码器

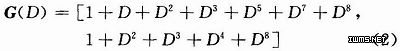

在CDMA 2000系统中,前向链路使用编码率为1/2,约束长度为9的卷积编码器。前向链路卷积码的生成多项式矩阵为:

由此生成多项式矩阵可得前向编码器的结构图,如图2所示。图中s1~s8为移位寄存器;m1,m2为模2和加法器;其中b1代表当前输入的信息位;移位寄存器状态b2~b9存储以前的信息位;c代表编码后的输出码元。