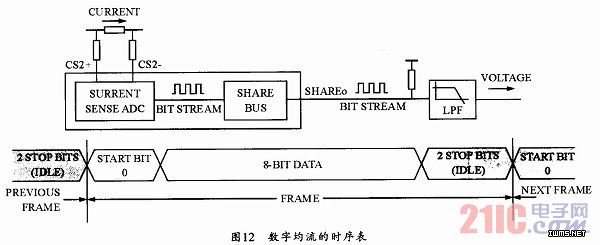

此位的长度固定在10μs,逻辑1定义到高到低的此位开始的传输。由低到高的传输在tBIT的25%处为低到高。

总线在高时tBIT的整个周期内是理想的(其他总线的激活都是非法的)。Glitches到tglitch时(200ns),不予考虑。

数字代表着电流信息有八位长度。ADP1043A用八位MSBS作CS1和CS2的读出器。用此读出作为数字。当读出均流总线在任何处都给出相符的时段到CS1,CS2的电流读出点。

(3)数字均衡总线等效电路

每个电源比较数字作为输出能力的供电到总线的数字。

1)Round1

在Round1,每个电源第一次位于MSB总线处,如果电源检测出其SMB为相同的值,它继续到Round2,如果检出值低于总线值,它就是从属电源。

当电源变成从属者,它停止与均衡总线通讯,因为知道它不是主导者,然后它增加其输出电压供出更多的电流。

如果两个单元有相同的MSB,它们由于继续Round2,因为它们都不是主导者。

2)Round2

在Round2,所有电源仍与总线上的MSB通讯,如果电源检测出其MSB少于总线值,这就意味着,此电源必须成为从属,并停止与总线通讯。

3)Round3到Round8

同样工作重复进行,直到8个Round允许电源比较其数字,以此方法决定每个单元的主或从。

2.23 数字均衡总线结构

数字均流总线可以有各种结构.均衡总线环路由寄存器0*29调节,让从属接近主导电源电流,可选择调节寄存器0*2A,初级测或次级测都能用电流均衡信号编程寄存器0*29。

负载线可以在PSU3之间,此时用数字均流总线,在遥检电压点和负载之间的最小阻抗15mΩ。

(未完待续)