因为TMR资源消耗较大,一般方法中由于布线以及表决器的实现,当粒度越小耗费的资源更多。文献提出了一种比较新颖的小粒度的方法,它对基于SRAM的FPGA的结构进行了一些改变(LUT及CLB结构),以小粒度来实现TMR但资源消耗却得到降低。

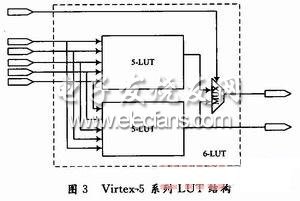

文中选用Xilinx Virtex-5系列芯片。其基本结构是由两个5输入的LUT实现的一个6输入的LUT。如图3所示。如果低五位输入数据相同那么可以实现两个5输入的LUT。在有些情况下,只需要5输入的LUT,此时另一个LUT没有被使用。如果在布局时使其总满足这种情况,那么可以用留下的资源来实现TMR。

一个TMR需要两个LUT,而两个TMR只需要三个LUT,需要在LUT内部实现表决器、报错电路以及其他的一些控制线,这增加了LUT内部的布线和延迟。

这种方法的优点是粒度减小,可靠性增加,资源消耗少,可通过检错和定位进行有条件的重构,减少了功耗和配置时间。实验结过表明,相比于传统的小粒度的TMR,这种方法额外资源消耗只为76.5%,而传统的则达到242%。

2.4 基于空间搜索方法的TMR技术

由于部分以及小粒度TMR的出现,在FPGA和设计约束的情况下,对粒度以及电路模块的选择是一个关键的问题,而往往只知道资源、功耗及可靠性等要求,实际的布局与实现是一个棘手的问题。文献都提出了基于空间搜索的方法。这种方法是提供资源、功耗与可靠性等参数,在各种可能的解决方法中进行搜索而得到最优的结果。

2.5 基于时间的TMR技术

基于时间的基本思想是通过多次计算进行故障屏蔽,是对相同的计算重复进行两次或者多次并比较结果以检测和克服错误。当对某一部分的电路得到一个结果后,暂时将其存储起来,延迟一定时间后再进行一次计算并输出存储,若比较结果不一致则出现了错误,此时再延迟相同的时间,将其输出作为正确的结果输出。

这种方法对于检测瞬时故障很有效,但其容错效果与延迟时间有关系。此方法实际上使用时间的延长换取了资源的节省,对于实时性较高的系统使用性较差。

2.6 基于软、硬件冗余的TMR技术

对于在硬件上出现的不可修复的损坏,上面的方法将都会失效。此时对每个模块中采用三个不同的版本的文件(一个使用,两个备份)且每个模块还有1/4的硬件冗余资源。如果出现了硬件故障,则首先用其他版本对其进行重新配置,如果这样问题还得不到解决,那么通过使用额外的冗余资源重新布局以绕过出错的部分。但是由于对冗余资源及存储单元的要求,这种方法进一步增加了资源的消耗。

3 TMR技术发展展望

基于以上的分析,用图4所示的框图来描述TMR技术出现的问题与改进方法之间的关系。由于硬件存在故障积累的问题,所以在系统可靠性的要求下产生出了多种新的基于TMR的解决办法,不过这些技术都只是针对某些问题而提出的,它只解决了部分问题同时也带来了一些新的问题,所以基于TMR的容错技术仍然不够成熟。

不过其中小粒度的TMR技术是一种灵活性很大的方法,它结合其他的一些方法可以在节约资源的基础上达到较好的性能,基于小粒度的TMR的技术将会是TMR技术的一个主要发展方向,需要进一步解决由于布线资源相对增多而对系统可靠性的影响。另外,由于小粒度TMR的实现需要对系统的各部分电路进行选择并进行布局,所以TMR实现的自动化也是一个需要研究的方向。

4 结语

总结了TMR技术存在的突出问题,研究了这些新方法,分析了其优势以及存在的问题并指出了相应的解决办法。TMR技术的发展应该以高效的实现方法及可靠性为方向,以稳健的评估策略为基础,根据所要达到的参数要求,以较高的自动化的方式在不同的粒度和布局上进行权衡而得到最终的TMR解决方案。