・上一文章:基于AT89S52多路数据采集系统的设计

・下一文章:基于LabWindows/CVI的数据库编程

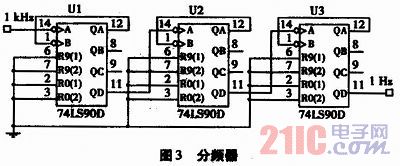

数字电子钟的时基信号是1 Hz,由555定时器产生的1 kHz的信号必须经过分频器才能获得1Hz的信号。分频器实际也是计数器,本设计中所用的分菝器有两个功能:一是产生标准1Hz的脉冲信号;二是提供校正电路的校正信号。因为74LS90是二-五-十进制计数器,所以采用三片计数器级联就可以实现上述功能,即三片级联可以获得所需的频率信号。电路图如图3所示。

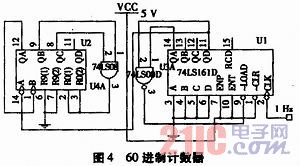

数字电子钟需要两个60进钊计数器分别作为“分”、“秒”计数器,还需要一个24进制计数器作“小时”计数器。60进制计数器采用一片74LS90和一片74LS161级联实现。74LS161用作“秒计数器”个位,所以将其设计成十进制计数器,这里用反馈预置法实现。即当计数器计到1001时,将74LS161的QA端和QD端,分别接至一个与非门的输入端,将与非门的输出端送至预置端LD,这样就可实现十进制计数。“秒计数器”的十位用74LS90实现,所以将其设计成六进制的计数器,用反馈清零法实现。即当计数器计到0110时,将74LS90的QB端和QC端,分别接至一个与门的输入端,将与门的输出端送至清零端R01和R02,由此实现六进制计数功能。其电路图如图4所示。