・上一文章:VC5402与外部存储器的接口设计

・下一文章:嵌入式多路信号数据采集系统

内部编码块DC 系数的反量化过程不同于其他的AC系数。DC 反量化系数由一个常数因子intra_dc 与QF[ 0 ][0]相乘而得到。intra_dc 与编码精度有关,表1 显示的即为两者对应关系。

AC 系数的反量化要用到两个加权矩阵,分别用于内部子块和非内部子块。用户也可以使用自定义的量化矩阵。

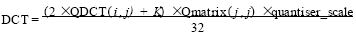

如果用QDCT 表示输入已量化的AC 系数,用DCT 表示反量化后的AC 系数,那么AC 系数的IQ 变换公式如下:

式中,quantiser_scale 为0~112 之间的两组数值,分别对应不同的比特流控制状态。但是在本系统采用的XviDCODEC 版本中,比特流控制功能并没有得到实现,所以这里quantiser_scale 的取值固定。

反量化得到的结果通过饱和化,使其限制在[ - 2048 ,+ 2047 ]之间。

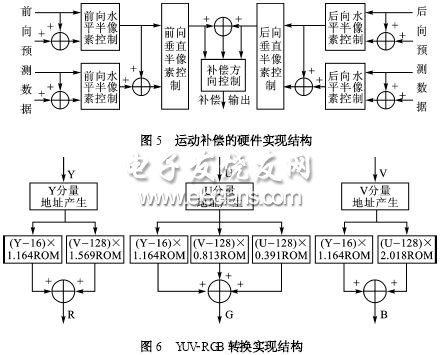

IQ 在FPGA 上按照图3 的框图进行硬件实现。

反离散余弦变换

IDCT 是DCT 的逆过程,用于还原DCT 系数矩阵。

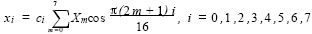

IDCT 过程可由下面的公式描述:

上式可视为一个2 个8 元向量的点积:

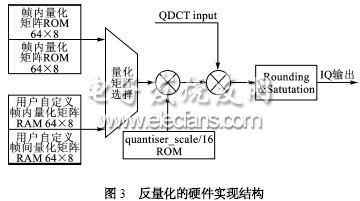

图4 反离散余弦变换的硬件实现结构

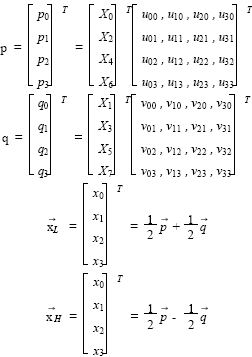

将8 元的输入向量[ X0 , X1 , X2 , X3 , X4 , X5 , X6 ,X7 ]分成奇元素[ X1 , X3 , X5 , X7 ]和偶元素[ X0 , X2 , X4 ,X6 ] ,8 ×8 矩阵则用2 个4 ×4 矩阵来代替,奇元素和偶元素分别与这2 个矩阵v 和u 相乘,生成2 个4 ×4 向量p 和q,通过加减向量p 和q ,可得到输出向量x。

算法可以表示成下面的公式:

基于8 ×8 矩阵的IDCT 算法,在FPGA 上按照图4所示的结构加以硬件实现。